- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: iMXRT1021 change FlexRAM size

iMXRT1021 change FlexRAM size

Dear all,

I have a trouble with FlexRAM resize.

Following reference Reallocating-the-FlexRAM , i can change IMXRT1021 ram size (ITC-OC-DTC) from default (64KB-128KB-64KB) to new value (64KB-64KB-128KB).

After flash program with Jlink, device can success boot up, run application without any problems.

When i call software reset (NVIC_SystemReset), device still booting up again and work fine.

But when i turnoff power source and turn on again, device never run to application success. Could you please give me your suggestion?

Thank you.

Edit1: With default RAM config, device can boot ok, booting problem only happen when i relocate FlexRAM

This is my configuration for relocate FlexRAM

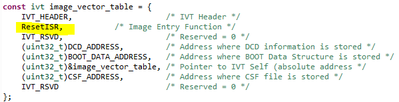

1. Reset handler

void ResetISR(void) {

// Disable interrupts

__asm volatile ("cpsid i");

// For debug only

volatile unsigned int IOMUXC_GPR_GPR17_Reg = *((unsigned int *) 0x400ac044);

volatile unsigned int IOMUXC_GPR_GPR16_Reg = *((unsigned int *) 0x400ac040);

//

/* Reallocating the FlexRAM */

__asm (".syntax unified\n"

"LDR R0, =0x400ac044\n" //Address of register IOMUXC_GPR_GPR17

"LDR R1, =0x00005FAA\n" //FlexRAM configuration DTC = 128KB, ITC = 64KB, OC = 64KB

"STR R1,[R0]\n"

".syntax divided\n");

__asm volatile ("MSR MSP, %0" : : "r" (&_vStackTop) : );

...........

}

2. MPU config for new FlexRAM configuration

/* Region 4 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(8, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_32MB);

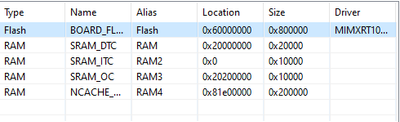

3. Linker option

4. XIP Nor option

已解决! 转到解答。

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

To provide the fastest possible support, I'd highly recommend you to use the below code instead of the original one and give it a try again.

void ResetISR(void) {

// Disable interrupts

__asm volatile ("cpsid i");

//FlexRAM reallocate: ITC-OC-DTC(64KB-64KB-128KB)

FLEXRAM->TCM_CTRL = 4;

IOMUXC_GPR->GPR17 = 0x0000FAA5;

IOMUXC_GPR->GPR16 |= 0x7;

IOMUXC_GPR->GPR14 = (8<<20) | (7<<16) ;

#if defined (__USE_CMSIS)

// If __USE_CMSIS defined, then call CMSIS SystemInit code

SystemInit();

#else

// Disable Watchdog

volatile unsigned int *WDOG1_WCR = (unsigned int *) 0x400B8000;

*WDOG1_WCR = *WDOG1_WCR & ~(1 << 2);

volatile unsigned int *WDOG2_WCR = (unsigned int *) 0x400D0000;

*WDOG2_WCR = *WDOG2_WCR & ~(1 << 2);

// Write watchdog update key to unlock

*((volatile unsigned int *)0x400BC004) = 0xD928C520;

// Set timeout value

*((volatile unsigned int *)0x400BC008) = 0xFFFF;

// Now disable watchdog via control register

volatile unsigned int *RTWDOG_CS = (unsigned int *) 0x400BC000;

*RTWDOG_CS = (*RTWDOG_CS & ~(1 << 7)) | (1 << 5);

#endif // (__USE_CMSIS)

//

// Copy the data sections from flash to SRAM.

//

unsigned int LoadAddr, ExeAddr, SectionLen;

unsigned int *SectionTableAddr;

// Load base address of Global Section Table

SectionTableAddr = &__data_section_table;

// Copy the data sections from flash to SRAM.

while (SectionTableAddr < &__data_section_table_end) {

LoadAddr = *SectionTableAddr++;

ExeAddr = *SectionTableAddr++;

SectionLen = *SectionTableAddr++;

data_init(LoadAddr, ExeAddr, SectionLen);

}

// At this point, SectionTableAddr = &__bss_section_table;

// Zero fill the bss segment

while (SectionTableAddr < &__bss_section_table_end) {

ExeAddr = *SectionTableAddr++;

SectionLen = *SectionTableAddr++;

bss_init(ExeAddr, SectionLen);

}

#if !defined (__USE_CMSIS)

// Assume that if __USE_CMSIS defined, then CMSIS SystemInit code

// will setup the VTOR register

// Check to see if we are running the code from a non-zero

// address (eg RAM, external flash), in which case we need

// to modify the VTOR register to tell the CPU that the

// vector table is located at a non-0x0 address.

unsigned int * pSCB_VTOR = (unsigned int *) 0xE000ED08;

if ((unsigned int *)g_pfnVectors!=(unsigned int *) 0x00000000) {

*pSCB_VTOR = (unsigned int)g_pfnVectors;

}

#endif // (__USE_CMSIS)

#if defined (__cplusplus)

//

// Call C++ library initialisation

//

__libc_init_array();

#endif

// Reenable interrupts

__asm volatile ("cpsie i");

#if defined (__REDLIB__)

// Call the Redlib library, which in turn calls main()

__main();

#else

main();

#endif

//

// main() shouldn't return, but if it does, we'll just enter an infinite loop

//

while (1) {

;

}

}Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

To provide the fastest possible support, I'd highly recommend you to use the below code instead of the original one and give it a try again.

void ResetISR(void) {

// Disable interrupts

__asm volatile ("cpsid i");

//FlexRAM reallocate: ITC-OC-DTC(64KB-64KB-128KB)

FLEXRAM->TCM_CTRL = 4;

IOMUXC_GPR->GPR17 = 0x0000FAA5;

IOMUXC_GPR->GPR16 |= 0x7;

IOMUXC_GPR->GPR14 = (8<<20) | (7<<16) ;

#if defined (__USE_CMSIS)

// If __USE_CMSIS defined, then call CMSIS SystemInit code

SystemInit();

#else

// Disable Watchdog

volatile unsigned int *WDOG1_WCR = (unsigned int *) 0x400B8000;

*WDOG1_WCR = *WDOG1_WCR & ~(1 << 2);

volatile unsigned int *WDOG2_WCR = (unsigned int *) 0x400D0000;

*WDOG2_WCR = *WDOG2_WCR & ~(1 << 2);

// Write watchdog update key to unlock

*((volatile unsigned int *)0x400BC004) = 0xD928C520;

// Set timeout value

*((volatile unsigned int *)0x400BC008) = 0xFFFF;

// Now disable watchdog via control register

volatile unsigned int *RTWDOG_CS = (unsigned int *) 0x400BC000;

*RTWDOG_CS = (*RTWDOG_CS & ~(1 << 7)) | (1 << 5);

#endif // (__USE_CMSIS)

//

// Copy the data sections from flash to SRAM.

//

unsigned int LoadAddr, ExeAddr, SectionLen;

unsigned int *SectionTableAddr;

// Load base address of Global Section Table

SectionTableAddr = &__data_section_table;

// Copy the data sections from flash to SRAM.

while (SectionTableAddr < &__data_section_table_end) {

LoadAddr = *SectionTableAddr++;

ExeAddr = *SectionTableAddr++;

SectionLen = *SectionTableAddr++;

data_init(LoadAddr, ExeAddr, SectionLen);

}

// At this point, SectionTableAddr = &__bss_section_table;

// Zero fill the bss segment

while (SectionTableAddr < &__bss_section_table_end) {

ExeAddr = *SectionTableAddr++;

SectionLen = *SectionTableAddr++;

bss_init(ExeAddr, SectionLen);

}

#if !defined (__USE_CMSIS)

// Assume that if __USE_CMSIS defined, then CMSIS SystemInit code

// will setup the VTOR register

// Check to see if we are running the code from a non-zero

// address (eg RAM, external flash), in which case we need

// to modify the VTOR register to tell the CPU that the

// vector table is located at a non-0x0 address.

unsigned int * pSCB_VTOR = (unsigned int *) 0xE000ED08;

if ((unsigned int *)g_pfnVectors!=(unsigned int *) 0x00000000) {

*pSCB_VTOR = (unsigned int)g_pfnVectors;

}

#endif // (__USE_CMSIS)

#if defined (__cplusplus)

//

// Call C++ library initialisation

//

__libc_init_array();

#endif

// Reenable interrupts

__asm volatile ("cpsie i");

#if defined (__REDLIB__)

// Call the Redlib library, which in turn calls main()

__main();

#else

main();

#endif

//

// main() shouldn't return, but if it does, we'll just enter an infinite loop

//

while (1) {

;

}

}Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------