- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- iMXRT FlexIO SPI CS high time between two transfers

iMXRT FlexIO SPI CS high time between two transfers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMXRT FlexIO SPI CS high time between two transfers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I would like to control an ADC chip via FlexIO SPI.

How can I influence the clock cycle between the slave select

negating and before the next transfer?

In SDK examples this time is always an SPI clock.

I need longer time for CS high before the next transfer started.

Is that possible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please help to provide the i.MXRT product detailed part number?

Then I will check with related SDK driver. Thanks.

Have a great day,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to control the AD7699 via FlexIO3 on an iMXRT 1060.

AD7699 should run in "read / write after convert" mode.

Need exactly 1.6us CS high between the data.

At a SPI clock e.g. 20MHz.

Thank you in advance,

Johann

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johann,

Sorry for the later reply.

I did a test with MIMXRT1060-EVK board with [flexio3_spi_int_lpspi_transfer_master] demo.

I could find your mentioned behavior.

I want to modify the Flexio spi driver at <fsl_flexio_spi.c> file FLEXIO_SPI_MasterInit() function without success.

So far, when customer write data to shifter buffer, the FlexIO_SPI engine will start to transfer data.

So, customer can set TRANSFER_SIZE to 1, which means only transfer one byte, and then call FLEXIO_SPI_MasterTransferNonBlocking function again to transfer another byte with related time interval.

#define TRANSFER_SIZE 1U /*! Transfer dataSize */

/*Start master transfer*/

masterXfer.txData = masterTxData;

masterXfer.rxData = masterRxData;

masterXfer.dataSize = TRANSFER_SIZE;

masterXfer.flags = kFLEXIO_SPI_8bitMsb;

isMasterTransferCompleted = false;

FLEXIO_SPI_MasterTransferNonBlocking(&spiDev, &g_m_handle, &masterXfer);

for(int i = 0; i<0xfff; i++)

{

asm("nop");

}

while (!(isMasterTransferCompleted))

{

}

isMasterTransferCompleted = false;

FLEXIO_SPI_MasterTransferNonBlocking(&spiDev, &g_m_handle, &masterXfer);

for(int i = 0; i<0xffff; i++)

{

asm("nop");

}

while (!(isMasterTransferCompleted))

{

}

isMasterTransferCompleted = false;

FLEXIO_SPI_MasterTransferNonBlocking(&spiDev, &g_m_handle, &masterXfer);

for(int i = 0; i<0xfff; i++)

{

asm("nop");

}

while (!(isMasterTransferCompleted))

{

}

isMasterTransferCompleted = false;

FLEXIO_SPI_MasterTransferNonBlocking(&spiDev, &g_m_handle, &masterXfer);

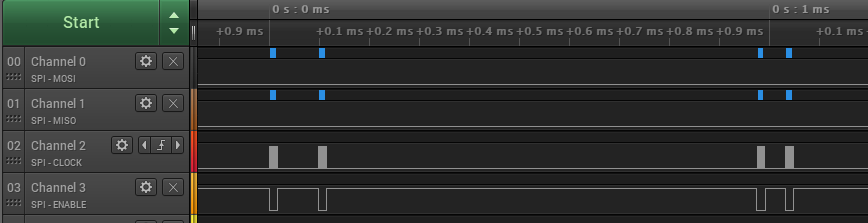

The test result is below:

I couldn't change the Flexio_spi low level driver, just called related API using a tricky way.

Thanks for the attention.

best regards,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mike,

thanks for the answer.

The idea is to control 4x the AD7699 with the FlexIO.

SPI-Enable, SPI-Clock and SPI-MOSI connected parallel to all ADC's,

just read in the MISO from each AD7699 via FlexIO extra.

Would that be possible in principle with FlexIO?

Can you give me a hint how to expand the existing driver?

best regards

Johann

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johann,

First of all, sorry for the later reply.

It is possible to use FlexIO with more MISO pins.

Please refer current <fsl_flexio_spi.c> file FLEXIO_SPI_MasterInit() function to add three more shifter for rx.

And it also need to set required pins with FlexIO function.

Wish it helps.

best regards,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mike,

I have implemented 2x AD7699 read in parallel SPI.

It works so far.

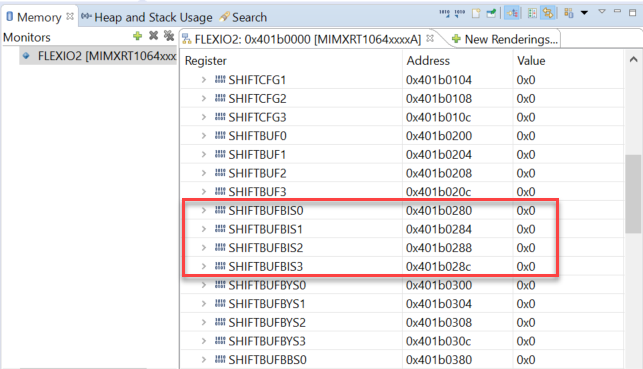

Only I was surprised that the SDK MIMXRT1064.h SHIFTBUFBIS [4] is limited to 4. In the i.MX RT1064 rtreference manual page 2925 the registers are described with SHIFTBUFBIS0 -

SHIFTBUFBIS7.

Is it a survival of the i.MXRT1060 or what's right there?

best regards

Johann

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johann,

Sorry for the later reply.

I did a test with MIMXRT1064-EVK board, the debug info showed there with 4 shifter with one FlixIO module.

The RT1064 reference manual with incorrect info.

I will report that document issue.

Thanks and have a nice day!

best regards,

Mike