- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- i.MX RT1060 Cannot Write to Flash

i.MX RT1060 Cannot Write to Flash

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are having issues writing to flash when booting using internal boot mode, but not when using JTAG. When booting with internal boot mode XIP_EXTERNAL_FLASH and XIP_BOOT_HEADER_ENABLE are both defined as 1. I am also sure that when booting, the program is transferred to SRAM_ITC, however I will include linker scripts just in case something isn't set correctly.

When trying to execute a write or erase command on the flash through FlexSPI, the status kStatus_FLEXSPI_IpCommandSequenceError is returned. Reading from flash works perfectly fine. From the reference manual, this status error means "IP triggered Command Sequences Error Detected interrupt. When an error detected for IP command, this command will be ignored and not executed at all".

I assume that since XIP_EXTERNAL_FLASH and XIP_BOOT_HEADER_ENABLE are both defined that the device, or the FlexSPI, or something must be set into XIP mode which will prevent any writing to flash. However I cannot see where this might be. If XIP_EXTERNAL_FLASH and XIP_BOOT_HEADER_ENABLE are not defined then we cannot run the program at all.

Thanks for any suggestions,

Nick

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In order to get my program to copy from NOR Flash into ITC RAM I followed this example https://mcuoneclipse.com/2019/01/22/tutorial-booting-the-nxp-i-mx-rt-from-micro-sd-card/ up until the point where they generate the .bin files from the .s19. I found that creating the SRAM_ITC_reserved partition was definitely required in order for the process to work. I'll include my .bd file (as .txt to allow it to upload) as the values that worked for me were different from the values in the tutorial as I was using NOR Flash instead of SD Card. XIP_EXTERNAL_FLASH and XIP_BOOT_HEADER_ENABLE are both defined as 0 in my project settings.

Once the .bin files are generated using the .bd file, I then combined the padded .bin and sip_flash_config.bin, located in "Flashloader_RT106x_1.0_GA\Tools\mfgtools-rel\Profiles\MXRT106X\OS Firmware" of the flashloader directory, to generate a full image. I did this because the padded .bin that was generated contains the application image at 0x2000 and the IVT at 0x1000, but the Flash Config Block at 0x0000 was empty and sip_flash_config.bin contains the FCB.

Having created my own full image, I then used the NXP MCU Boot Utility (https://github.com/JayHeng/NXP-MCUBootUtility) to load the image into my flash device. In the Boot Utility, the Application Image File was set to Raw Binary with base address 0x00000000. Now my program was booting from ITC RAM, I could initialise the FlexSPI as if running a JTAG session and all Flash operations (read/write/erase) work perfectly fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In order to get my program to copy from NOR Flash into ITC RAM I followed this example https://mcuoneclipse.com/2019/01/22/tutorial-booting-the-nxp-i-mx-rt-from-micro-sd-card/ up until the point where they generate the .bin files from the .s19. I found that creating the SRAM_ITC_reserved partition was definitely required in order for the process to work. I'll include my .bd file (as .txt to allow it to upload) as the values that worked for me were different from the values in the tutorial as I was using NOR Flash instead of SD Card. XIP_EXTERNAL_FLASH and XIP_BOOT_HEADER_ENABLE are both defined as 0 in my project settings.

Once the .bin files are generated using the .bd file, I then combined the padded .bin and sip_flash_config.bin, located in "Flashloader_RT106x_1.0_GA\Tools\mfgtools-rel\Profiles\MXRT106X\OS Firmware" of the flashloader directory, to generate a full image. I did this because the padded .bin that was generated contains the application image at 0x2000 and the IVT at 0x1000, but the Flash Config Block at 0x0000 was empty and sip_flash_config.bin contains the FCB.

Having created my own full image, I then used the NXP MCU Boot Utility (https://github.com/JayHeng/NXP-MCUBootUtility) to load the image into my flash device. In the Boot Utility, the Application Image File was set to Raw Binary with base address 0x00000000. Now my program was booting from ITC RAM, I could initialise the FlexSPI as if running a JTAG session and all Flash operations (read/write/erase) work perfectly fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey nick,

after creating the bin files with your .bd file I have two files: application.bin and application_nopadding.bin.

Did you take the sip_flash_config.bin first and application.bin second and concatenate them into one file (called full_image.bin for examle) ?

And then you load the output with the NXP MCU Boot Utility?

Best regard

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ofirs,

Once the two files are created (application.bin and application_nopadding.bin) I take application.bin and sip_flash_config.bin and overwrite the beginning of application.bin with the whole sip_flash_config.bin. This would then be called fill_image.bin and I use that to load into flash using NXP MCU Boot Utility at the base address of the flash.

Hope this helps,

Nick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello nick_j,

running an application via debugger and running it after power on reset (POR) is slightly different. After POR the ROM-Code is initializing some peripherals especially the FlexSPI-Interface. When running on JTAG, the Development Environment may or may not initialize also some stuff (maybe different).

How does your initialization of your Flex-SPI interface look like? After POR the FlexSPI Interface should already be initialized for reading (needed for XIP). For writing and erasing you must update the LUT with the respective command sets to be able to write/erase

For a running via debugger, you must initialize the whole interface.

Hope this helps

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Masmiseim ,

Thanks for your reply. I have managed to resolve the issue using this tutorial https://mcuoneclipse.com/2019/01/22/tutorial-booting-the-nxp-i-mx-rt-from-micro-sd-card/ but modifying it slightly as I'm using NOR flash instead. I think the main issue of writing to flash was that the program was still technically running XIP and not truly copying to SRAM. Once booting from SRAM, the FlexSPI could be initialised as if running from JTAG and there have been no issues since.

Thanks again for your reply,

Nick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nick,

The following community document explains how to generate a bootable image that is copied into the internal SRAM.

Generating a Bootable Image for the RT1050 - NXP Community

The section that explains this is called "Bootable Image Generation – SRAM". If you follow this procedure, does your example work correctly? How are you initializing and configuring the flash in your application?

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Victor,

Thanks for your reply. I have managed to resolve the issue using this tutorial https://mcuoneclipse.com/2019/01/22/tutorial-booting-the-nxp-i-mx-rt-from-micro-sd-card/ but modifying it slightly as I'm using NOR flash instead. I think the main issue of writing to flash was that the program was still technically running XIP and not truly copying to SRAM. Once booting from SRAM, the FlexSPI could be initialised as if running from JTAG and there have been no issues since.

Thanks again for your reply,

Nick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

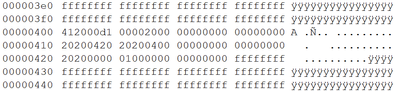

I have edited the vector table in my .bin file based on the application note linked below. The MCUBootUtility complains about an invalid address in vector table however. We cannot see why this table is incorrect.

https://www.nxp.com/docs/en/nxp/application-notes/AN12238.pdf