- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: i.MX RT1010 GPT behavior

i.MX RT1010 GPT behavior

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

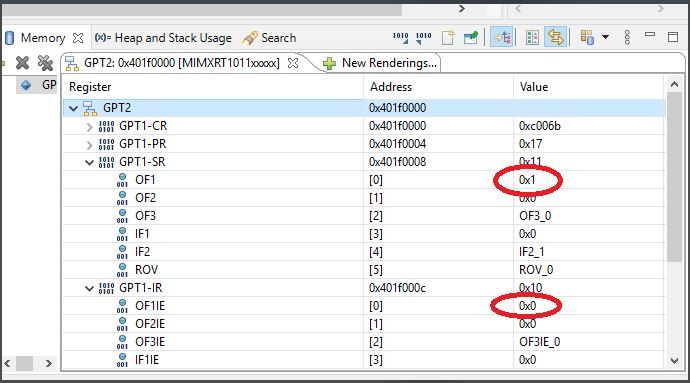

I am debugging on RT1010 Evaluation Kit which uses GPT2 module,

Some unexpected interrupts of Output Compare occurred (OF1 sets to 1) even the interrupt control bit OF1IE is not enabled. Is that possible?

Other issue is, the register names under GPT2 group are with prefix GPT1 such GPT1-IR, GPT1-SR, I am not use if it causes any issue or just the name convention.

The issue has taken me quite lot of time, looking for your helps.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Babycat,

Thanks for your updated information.

In fact, no matter the compare or the capture, the situation is the same.

OFn or IFn is means the event has occurred on compare or capture, but the OFnIE or IFnIE is in the GPT interrupt register, it is means one gate, when the OFn is set, whether it generate the interrupt or not.

So, you can consider OFn is the event happens, not determined by OFnIE or IFnIE, OFnIE or IFnIE is the interrupt generate gate. If you not set OFnIE or IFnIE. You still can use while to checking OFn or IFn is setting or not, to determine whether the actual even is happening.

Wish it helps you!

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

Sorry for late reply.

First of all, my critical typing mistake "Some unexpected interrupts of Output Capture occurred (OF1 sets to 1) even the interrupt control bit OF1IE is not enabled. Is that possible?"

The correction is: "Some unexpected interrupts of Output Capture Compare occurred (OF1 sets to 1) even the interrupt control bit OF1IE is not enabled. Is that possible?" That might led you misunderstood my question.

Yes, I know that Input Capture and Output Compare are independent to each others.

My issue was about OF1 and OF1IE. I still can't configure out how the interrupt flag is set (OF1 =1) while its interrupt is not enabled (OF1IE =0)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Babycat,

Thanks for your updated information.

In fact, no matter the compare or the capture, the situation is the same.

OFn or IFn is means the event has occurred on compare or capture, but the OFnIE or IFnIE is in the GPT interrupt register, it is means one gate, when the OFn is set, whether it generate the interrupt or not.

So, you can consider OFn is the event happens, not determined by OFnIE or IFnIE, OFnIE or IFnIE is the interrupt generate gate. If you not set OFnIE or IFnIE. You still can use while to checking OFn or IFn is setting or not, to determine whether the actual even is happening.

Wish it helps you!

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Babycat,

Thank you for your interest in the NXP MIMXRT product, I would like to provide service for you.

About this question, please help to confirm the SDK version and the code:

SDK_2.9.1_EVK-MIMXRT1010\boards\evkmimxrt1010\driver_examples\gpt\timer

This project, right?

And you are using MCUXpresso 10.3.0, right?

Tomorrow, I will find time to test it on my side, then give your deep testing reply, please keep patient, thanks so much for your understanding.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry

Thanks for your support,

I am using MCUXpresso IDE v11.3.0 [Build 5222] [2021-01-11], SDK 2.9.0 (435 2021-01-12).

FYI: I switched to GPT1, but somehow is same behavior.

My project is cloned from evkmimxrt1010\driver_examples\gpt\timer.

Please help to test and update us.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Babycat,

Sorry for my later reply, because of a lot of cases in the testing queue these days.

Today, I tested your mentioned GPT project, now answer your questions:

1. Some unexpected interrupts of Output Capture occurred (OF1 sets to 1) even the interrupt control bit OF1IE is not enabled. Is that possible?

Answer: yes, it's possible!

OF1 set to 1, just means GPT status register is updated, IF1 Input capture 1 Flag, it means the input capture1 already has the capture event, the GPT IP get the event. It's totally not determined by the OF1IE. Please note, OF1IE is OF1IE Output Compare 1 Interrupt Enable.

It means, if you enable this bit, then when the OF1 is 1, then it will enter the interrupt.

But if your OF1IE is 0, just means you didn't enable the interrupt, but your GPT capture function already works, and it already gets the capture event, then you also can use the software to check the OF1 flag, and do the related capture things.

So, this is not the issue!

2. Other issue is, the register names under GPT2 group are with prefix GPT1 such GPT1-IR, GPT1-SR, I am not use if it causes any issue or just the name convention.

Answer: You are right, I think it is the MCUXPresso IDE register description issues, in fact, under GPT2, it just need to use GPT instead of GPT1.

I will report to our MCUXPresso IDE department, and it will be fixed in the next version.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry