- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: IMXRT1062 Hardfault Reading CAN3 ERFCR Register

IMXRT1062 Hardfault Reading CAN3 ERFCR Register

IMXRT1062 Hardfault Reading CAN3 ERFCR Register

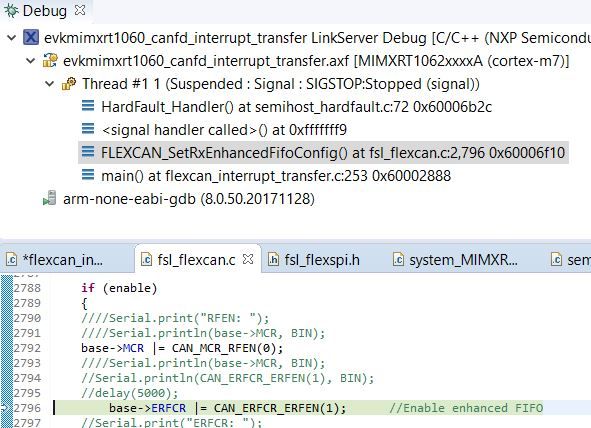

According to the 1060RM setting the ERFCR will enable the Enhanced FIFO. However when I try to even read the register in the FLEXCAN example it throws a hard fault. When I tried it in my own application on a imxrt1062 I also get a hard fault at that register address. Needless to say I can't set it either.

So the question is, what is the cause of the issue and is Enhanced FIFO even enabled and the RM is incorrect?

Before you call base->ERFCR |= CAN_ERFCR_ERFEN(1);

Please note this point:

MCR[RFEN] must be cleared so that Enhanced Rx FIFO is enabled.

I find your code didn't add the MCR[RFEN] clear code, please add it and try it again.

BTW, it's better to provide the source code, because I even can't find your definition about:flexcan_fd_fifo_filter_b01_t

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Did you check to see what other registers in the Flexcan controller can be read? Which ones can and which ones can't may point to the problem.

> base->ERFCR |= CAN_ERFCR_ERFEN(1);

Are you sure the compiler isn't turning that into a bit or byte operation? Can you disassemble it and see what it is really doing?

The definition of the address of "ERFCR" also relies on a lot of definitions in the headers being right, and six sets of "uint8_t RESERVED_N[MMM]" being parsed properly. Can you print the address you're actually accessing to see if it is correct?

Tom

Hi Tom

Well right before the fault I print several registers as a sanity check of the configuration:

MCR ---- a0080f

CTRL1 ---- 15a2021

TIMER ---- cdd

IMASK1 ---- 0

IFLAG1 ---- 0

IFLAG2 ---- 0

CTRL2 ---- b30000

ESR2 ---- 6000

CRCR ---- 0

ESR2 ---- 6000

FDCTRL ---- 80008300

CLOCKS

CCM_CSCMR2 ---- 13192e0e

CCM_CCGR7 ---- fffffff3

Also, I have run the CANFD examples without a problem so know at least the normal registers are working.

As for "> base->ERFCR |= CAN_ERFCR_ERFEN(1); " I tried it this was as well "> base->ERFCR = CAN_ERFCR_ERFEN(1); " and will still get the fault.

Ok you got me on this one: "six sets of "uint8_t RESERVED_N[MMM]" being parsed properly. Can you print the address you're actually accessing to see if it is correct?" - this is what I get

ERFCR -------401d8c0c which is correct to the manual.

Can I ask you all another question - i tried adding printf in the driver itself but the compiler complained - can you tell me how to do that?

Thanks

Mike

> Can I ask you all another question - i tried adding printf in the driver itself but

> the compiler complained - can you tell me how to do that?

I think you edited the post because there are changes between it and the email notification I received. I'm guessing you found the "%p" option in "printf()" or cast the address to an int or something.

I don't know what operating system you're running (assuming it isn't Linux on these parts), so don't know what calls they're using for this. How to debug-print from a driver should be documented somewhere. Assuming it isn't, or you can't find it, read the other drivers until you can find some debug printing that a previous author left in there, and copy that. That driver may be including a header that is required for the functions it uses, so you'll have to check through the header sources to find which ones are needed, or just include all of them (that the other driver does) and start deleting them to find out which one or ones it needs.

Tom

Hi Michael Smorto,

Thank you for your new code.

Do you port your code to the SDK canfd_interrupt project, now, could you tell me, what the detailed problem in your attachment, still enter the hard fault? Which code line will enter the hard fault, then I will help you to test it on my board.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Kerry

Just reran. Yep it hard faults at enabling the enhanced FIFO. Here's a little screenshot:

I know there are other problems with my coding for Enhanced FIFO, but need to get past this first. Thanks for all your help.

Respectfully

Mike

Hi All

Haven't heard anything on this issue for awhile so was wondering if there is any status or is it just not possible to do FIFO FD on the 1062.

Hi Kerry

Sorry I didn't get back to you sooner but wrapped up in some other testing yesterday. Anyway, I cleared MCR[FREN] bit and double checked that it was cleared by outputting the register in binary. Matter of before clearing the bit I checked and it was already cleared. But anyway, I do have to advise you that I already know that I am sure there are errors in my implementation for Enhanced FIFO but figured it would debug those going forward.

Anyway here is the whole source code.

Can you read the registers at offset zero? Can you read all the registers from 0x00 to 0x50?

... the MBs from 0x80 to 0x47f?

... the RXIMRs from 0x880 to 0x87c?

... 0xbf0 to 0xbfc?

... 0xc00 to 0xc14?

... 0xc30 to 0xd2c?

... 0x2000 - 0x204c?

... 0x3000 - 0x31fc?

Are you sure "CAN_MCR[RFEN]" isn't set?

Does the module have all of its clocks generated and enabled (Table 13-5 and CCM_CCGR7?

Tom