- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- Identification and Security

- i.MX Processors

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- CodeWarrior

- Wireless Connectivity

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: IMXRT1060 and SRAM in synchro mode

IMXRT1060 and SRAM in synchro mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMXRT1060 and SRAM in synchro mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All.

I am working with iMXRT1060 and want to use SRAM in synchronous mode via SEMC.

Can anybody give me an example or link how to work with SRAM in synchro mode?

Thanks in advance.

Regards,

George.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank your very match, Melissa.

I use SEMC/SRAM in sync mode to interface with FPGA, and have some strange time gaps between burst transfers.

I transfer 1Kb of data from/to SRAM at 0xA000xxxx to/from OCRAM at 0x2020xxxx using DMA engine.

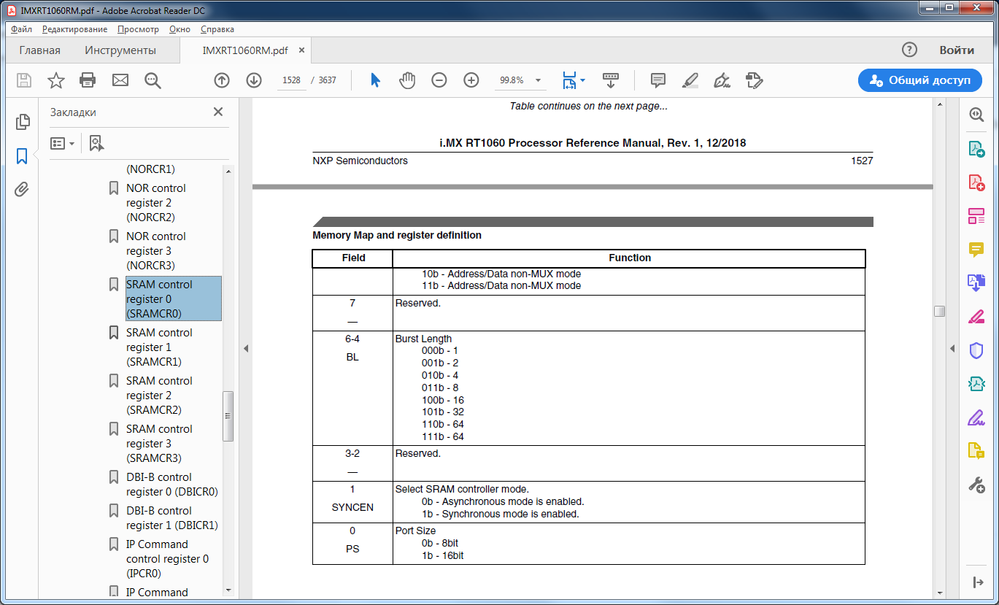

SEMC parameters: sram sync mode, 16 bit, mux A/D, zero all waits, BL=4(->burst16), LC=4(latency).

// SEMC->SRAMCR0=0x0000F043; ..SRAMCR1=0x00000000; ..SRAMCR2=0x00040000;

DMA transfer size is 32 bytes (it is a maximum, as I can understand).

Clocks: 150MHz SEMC, 150MHz IPG, 600MHz CPU.

As a result, I have timings for 1Kb transfers (and see 2x slow speed than expected):

Up (SEMC => OCRAM): burst16 time 170ns; gap time 170 ns; overall 1Kb time 11us;

Down (OCRAM => SEMC): burst16 time 150ns; gap time 170 ns; overall 1Kb time 10us;

Time diagram inside bursts seems Ok, but what about time between transfers?

The question is: are this time gaps "normal" for iMX1062 chip or I can do something to decrease them?

Sincerely yours Ivan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ivan,

I want to clarify a few things on your settings. You said the DMA transfer size is 32bytes. Is that actually the SSIZE/DSIZE and the overall transfer size (NBYTES) is 1Kb? It might be easiest if you just send me a screenshot showing the DMA TCD registers for the channel you are using. Then I can see the exact configuration you are using.

It won't help to decrease gaps between transfers, but is using a larger BL within the SEMC an option? Or does the FPGA not support it? For BL=4, I'm expecting 4 beats of 16-bits, so 8bytes per burst. Is this what you are getting? Are you seeing 16byte/8 beat bursts (which is why you are referring to it as burst16)?

Regards,

Melissa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Melissa.

Yes, I see this transfer 1Kb as 32 bursts by 16 words on 16 bit bus. Burst length coding as 4 in BL field of SRAMCR0 means 16 burst length.

I have and attach DMA,SEMC,CCM register logs, DMA used slot #4.

If, as you writing, gaps between transfers are " as-is ", we only can upset about this...

I see the BL field of SEMC.SRMCR0 can be tuned for 32 and 64 burst length - are this values can be actually used in this chip?

(what a process can activate so large transfers - DMA can`t move more then 32 bytes, as I see)

Thank you, Ivan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ivan,

Thanks for the registers, I understand your setup now. For the burst length, I was interpreting BL=4 as field configured for 010b which decodes to 4 instead of set to 100b which decodes to 16. Now that I can see your settings it is clear.

So you already have the SEMC configured for 32byte bursts (16 beats where each beat is 16-bits). The larger burst lengths won't help in your case. If you were using an 8-bit wide bus, then the BL=32 setting could be useful but for a 16-bit wide bus the BL=32 or 64 settings won't help, because as you said there isn't anything in the chip that would request transfers of this size.

The DMA configuration also looks good (SSIZE and DSIZE both set for 32-bytes). Unfortunately, I don't see anything obvious you can do from a configuration stand-point to speed things up.

Are you using the OCRAM space for any data, code, or stack that the core would be accessing while the DMA is running? The OCRAM is shared, so if the core (or any other masters on the chip) are also running accesses to the OCRAM while the DMA is running, then that could be adding delay (although the fact that you are seeing such a consistent gap between SEMC cycles makes it unlikely this is the case). If the core is accessing the OCRAM while the DMA is running, then you could either move what the core is accessing to a different RAM (to avoid the DMA potentially having to wait to get access to the OCRAM). Another option is to adjust the internal bus priority using the NIC, but the bus priority is only used if both masters are trying to start an access at the same time. If the core is already running an access to the OCRAM when the DMA wants to write to OCRAM, then the DMA does have to wait for the core access to complete (higher priority request won't abort a transaction in progress).

Hope this helps,

Melissa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @melissa_hunter,

Excuse me for cutting in,

Your comments are very helpful to us.

We would like to use the RT1175 SEMC to connect to the FPGA with SYNC SRAM non-ADMUX mode.

Our concern is that when reading data from our FPGA, the data length may not be 16 word boundary.

This is a possibility, but please tell me.

If DMA SSIZE/DSIZE = 32byte and SEMC BL<16 beats, How can you expect the SRAM bus cycle to behave?

Will multiple bus cycles be issued?

Or will it trigger a fatal error such as Hard Fault?

What happens when BL>16?

It may be a strange question, but we want to hear your opinion.

BR,

George

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very match, Melissa,

I check my process for some concurrency from CPU, but, find nothing...

CPU only waits DMA ready, runs at code addresses 0x0001xxxx ( TCM ) and only accesses DMA0 registers;

Moreover, if I do 32-bit transactions (when I waiting DMA finish) from CPU to FPGA , they "placed inside gaps", practically no increasing overall process time. It seems, DMA engine pauses without any need...

Ivan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ivan,

Unfortunately I think you've done what you can to optimize, so the performance you're getting is it.

Regards,

Melissa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Melissa.

Best regards,

Ivan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Geroge,

The only example we have available is the SEMC example of the MCUXpresso SDK. The sdramc example shows how to use SEMC controller driver to initialize the external SDRAM chip. Please use it for reference.

I hope it helps!

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Felipe,

I see a lot of settings in the SEMC according SRAM sync mode, all of

them are not described.

There are:

- SRAMCR0.COL

- SRAMCR3.RDH

- SRAMCR3.CEITV

- SRAMCR3.RD

- SRAMCR3.WDH

- SRAMCR3.WDS

Can you ask R&D group describe them and give me diagrams to see them?

Thanks in advance.

George Volokh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi George,

I am going to ask internally to see if we have some example that we can share. I will let you know if there is any update.

Regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Felipe,

Thanks a lot, it will be very nice.

In other case, it will be too strange to have such powerful chip and not

to have information how to use it.

Thanks in advance,

Regards,

George Volokh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi George,

I have received feedback from the applications team and unfortunately, we do not have any SRAM example that we could provide.

I am sorry for the inconvenience that this may cause you.

Regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi George,

Do you still need help with this? As Felipe stated, we don't have any SRAM examples. I can help you as best I can though (I don't have a board with an SRAM to use for testing). If you do still need help with the SRAM, let me know how far you've gotten and what problems/questions are open.

Regards,

Melissa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Melissa,

are the questions about SRAM performance must be started in a new thread?

Or I can join and continue here?

Ivan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ivan,

You can just add your questions to this thread if you want.

Regards,

Melisa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank your very match, Melissa. I start as a reply to George to remove spare tabs...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Melissa,

Thanks again for your very professional support.

We are working with SRAM in synchronous mode (really we connect an FPGA

via this bus).

Everything is working now, but we are trying to speed up the communication.

And, as I know, it doesn't work fast.

I will ask my college Ivan Osipov to connect to you, he is in charge of

this part of our device.

He is in copy.

Thanks and regards,

George Volokh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Felipe,

Really it doesn't help and it was a reason to ask you the question.

SDRAM works nice here, but I can run SRAM using SEMC.

Can you ask your R&D group for an example?

Thanks in advance.

George Volokh.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Felipe,

Really it doesn't help and it was a reason to ask you the question.

SDRAM works nice here, but I can run SRAM using SEMC.

Can you ask your R&D group for an example?

Thanks in advance.

George Volokh.