- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- I.mxRT1020 GPIO_SD_B1_05 (Pin 26) HardFault

I.mxRT1020 GPIO_SD_B1_05 (Pin 26) HardFault

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.mxRT1020 GPIO_SD_B1_05 (Pin 26) HardFault

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear I.mxRT1020 support,

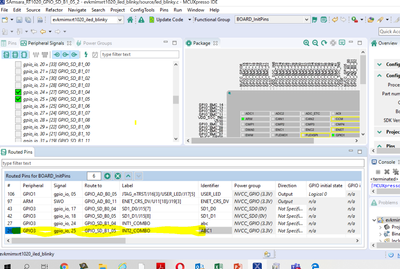

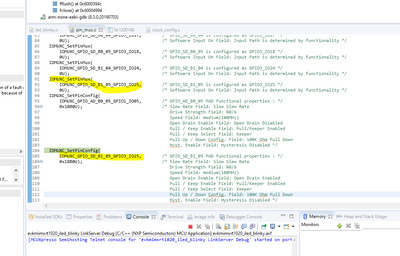

It seem that whenever I tried to enable the GPIO_SD_B1_05 in using the code generated by the PInmux tool, it would generate a hard fault imediately after executing the next line after

IOMUXC_SetPinConfig(

IOMUXC_GPIO_SD_B1_05_GPIO3_IO25, /* GPIO_SD_B1_05 PAD functional properties : */

0x18B0U);

I am using IDE version 11.2 and SDK2.8.

Regards,

hy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

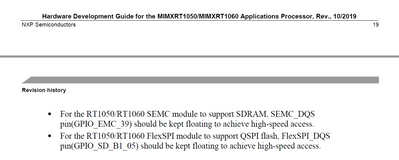

Also see this note from the hardware development guide

-Nick

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you to both for your quick reply.

I was wondering if you can let the design make a slight modification on his schematics to add a dQS signal name to the GPIO_SDS_b1_05 similar to the RT1050EVKB schematics.

It would help reduce the chance to make the same mistake for the next RT1020 customer.

Regards,

hy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

You can still use the pin but with reduced FlexSPI speed of 60MHz. If the code is not large it should be running from internal instruction RAM anyway where it achieves 500MHz with zero wait states and thus much faster than XiP mode (with less radiation and power consumption too).

Regards

Mark

uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training or product development requirements

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

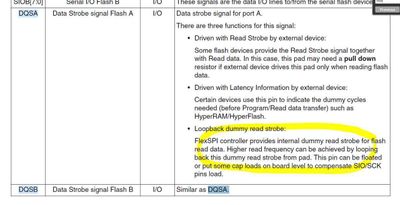

For QSPI Flash as XIP function, to achieve highest performance it is recommended to left FLEXSPI_A_DQS(GPIO_SD_B1_05)pin floating and config-sample clock source as 01-loopback from DQS pad mode to achieve max 133MHz Flexspi_clk, and change the function of this pin will make the application code crash.

Hope this clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

1) Can you confirm with the designer to see that is the case?

-- The DQS pin design suggestion definitely applies to QSPI flash, as I remember that AE highlighted this design tip during the RT training.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Jeremy,

I spoke with Anthony Huereca and also looked closer at Reference Manual.

It stated that the DQSA pin is only applicable for HyperRam/HyperFlash for dummy ready cycle.

For QSPI it doesn't apply. Can you confirm with designer to see that is the case?

If DQSA is not applicable for QSPI flash then we do have a conflict issue to resolve.

Thx,

hy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

The answer is here (same for i.MX RT 1020 and 1060 - You need to change the flash configuration to not use this pin and then it won't fail).

Regards

Mark

uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training or product development requirements

For a complete boot loader concept for your target check out the following:

- i.MX RT 1060: https://www.utasker.com/iMX/RT1060.html

- Boot loader concept including XiP on-the-fly decryption, clone protection or AES256 protected RAM execution.

-- Boot Loader concept flow chart: https://www.utasker.com/docs/iMX/Loader.pdf and usage reference https://www.utasker.com/docs/iMX/uTaskerLoader_TestDrive.pdf

-- Serial Loader features: https://www.utasker.com/docs/uTasker/uTaskerSerialLoader.pdf

-- Building the loader with MCUXpress: https://www.utasker.com/docs/iMX/MCUXpresso.pdf (and video guide https://youtu.be/p_eUGo6GypY ) - the guide document explains how to use with any application (eg. SDK) and to enabling its operation with On-The-Fly decryption in 5 minutes

-- Building the loader with IAR: https://www.utasker.com/docs/iMX/IAR.pdf (and video guide https://youtu.be/XPCwVndP99s )

-- Building the loader with VisualStudio and GCC: https://www.utasker.com/docs/iMX/GCC.pdf (and video guide https://youtu.be/0UzLLSXABK8 )