- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: How to config RT1170 EVK to use on chip RAM only?

How to config RT1170 EVK to use on chip RAM only?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all

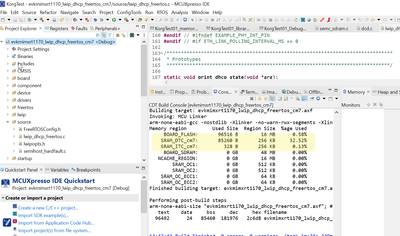

I am using EVK1170 and test with lwip_dhcp_freertos_cm7 example.

I noticed it use external RAM by default, and I would like to config the project use internal RAM only, as my target board won't have any external RAM. Please let me know the procedure for that.

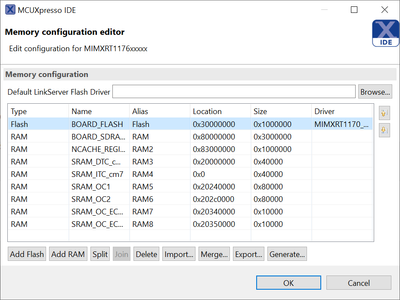

I tried remove delete RAM and RAM2 only from the memory editor below? what else do I need to do please?

Thank you!

Ping

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

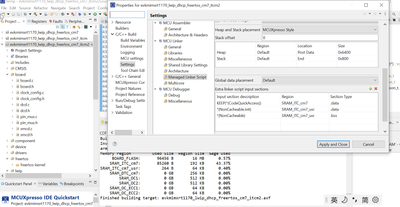

ITCM for NonCacheable setting also works on my side, please check my test result and the attached demo which I have written for you:

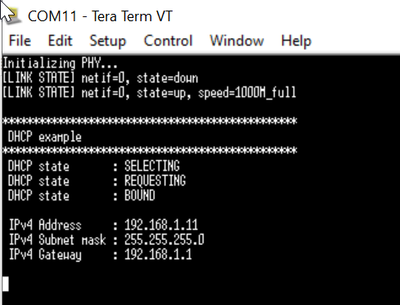

This is my DHCP test result:

You can test it on your MIMXRT1170-EVK board.

Wish it helps you!

BTW, 2024 Chinese Spring Festival: Feb 9th to Feb 18th in total 10 days.

We will in the Spring Festival vacation, and back to work from 2.19th. During this time, you also can create the case, then our Mexico colleague will help you in your new case.

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi I am trying to run "evkbmimxrt1170_lvgl_demo_widgets_cm7" without SDRAM but facing problem. It is a UI application.

My question is: Is it possible to run "evkbmimxrt1170_lvgl_demo_widgets_cm7" or any scalable GUI/UI application without external RAM.

For above configuration I am getting following errors:

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: evkbmimxrt1170_lvgl_demo_widgets_cm7.axf section `.bss_RAM2' will not fit in region `SRAM_ITC_cm7_user'

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: evkbmimxrt1170_lvgl_demo_widgets_cm7.axf section `.bss' will not fit in region `SRAM_ITC_cm7'

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: section .bss_RAM2 VMA [00030000,0023001f] overlaps section .bss VMA [00000440,003f5e57]

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: region `SRAM_ITC_cm7' overflowed by 3964504 bytes

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: region `SRAM_ITC_cm7_user' overflowed by 2031648 bytes

../com.nxp.mcuxpresso.tools.win32_11.9.0.202307121226/tools/bin/../lib/gcc/arm-none-eabi/12.3.1/../../../../arm-none-eabi/bin/ld.exe: ./board/board.o: in function `BOARD_ConfigMPU':

Memory region Used Size Region Size %age Used

BOARD_FLASH: 575592 B 64 MB 0.86%

SRAM_ITC_cm7: 4161112 B 192 KB 2116.45%

SRAM_ITC_cm7_user: 2097184 B 64 KB 3200.05%

SRAM_DTC_cm7: 0 GB 256 KB 0.00%

SRAM_OC1: 0 GB 512 KB 0.00%

SRAM_OC2: 0 GB 512 KB 0.00%

SRAM_OC_ECC1: 0 GB 64 KB 0.00%

SRAM_OC_ECC2: 0 GB 64 KB 0.00%

collect2.exe: error: ld returned 1 exit status

make[1]: *** [makefile:117: evkbmimxrt1170_lvgl_demo_widgets_cm7.axf] Error 1

make: *** [makefile:108: all] Error 2

"make -r -j4 all" terminated with exit code 2. Build might be incomplete.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mdkhaledibnhassan ,

If you have any issues, please help to create your own question post, then we will help you in your own question post, don't just follow your question in the other customer's closed post, thanks a lot for your understanding.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

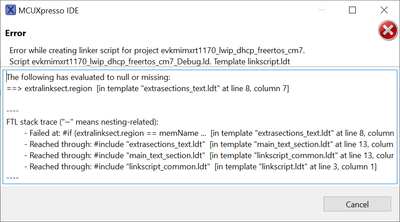

Just tried and got an error in compiling like below:

Help is needed please.

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

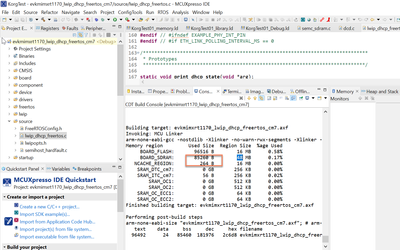

It's easy to realize it, please check the original project build result:

We can see, the used SDRAM size is about 84KB, so, totally can put to the internal RAM.

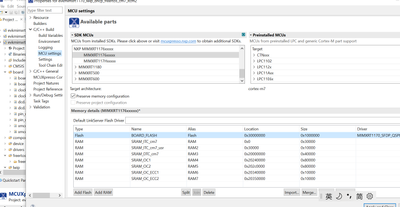

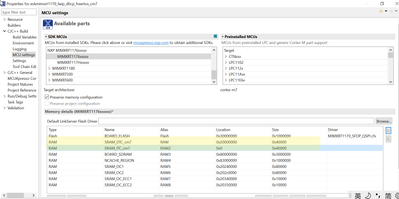

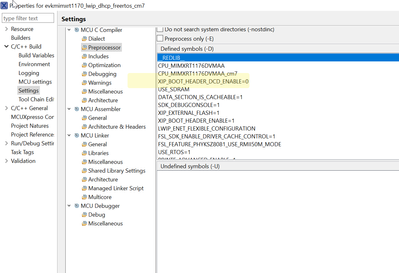

Then, you can change the memory setting like this:

Then the new build result is:

You can see, all the used data in the internal RAM now.

You can try it on your side.

BTW, you can remove XIP_BOOT_HEADER_DCD_ENABLE define to avoid the SDRAM definition:

About your remove the SDRAM memory situation, it is mainly related to the board.c:

extern uint32_t __base_NCACHE_REGION;

extern uint32_t __top_NCACHE_REGION;

uint32_t nonCacheStart = (uint32_t)(&__base_NCACHE_REGION);

uint32_t size = (uint32_t)(&__top_NCACHE_REGION) - nonCacheStart;

You can change the memory also to the ITCM or DTCM, then you will build without any issues.

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kerry

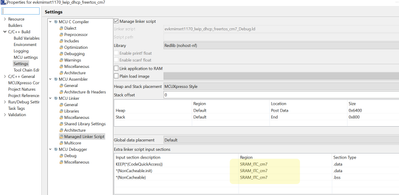

Thanks for reply, followed and found an issue with it, in Managed Linker Script section configure the NonCacheable.init and NonCacheable to SRAM_ITC_cm7 will cause a failure in fsl_component_serial_manager.c at line 1245 - assert(handle), handle is in ITC memory location 0 and it stays there forever. Change to DTC and works

I have been caution to use ITC memory for variables, it caused issue for me in past when use RT1024, here is another one. Although this one can be solved by change the remove the assert(). My question is can we use ITC like DTC ? is it used by CPU for other tasks?

Another question about the board.c definition for nonCacheStart and size, look like we have to define a location for it? why?

Thank you!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

Thanks for your updated information.

To the variables, it's better to put in the DTCM, as it is data TCM.

If you want to use the ITCM, I think, maybe also can define some special area in the ITCM from the TOP side, not the 0 addres, just dived the ITCM into two pieces, then define your used area in your own defined TCM area.

To the nonCacheStart, normally it is used for the SDRAM which need to use the nonCache area, as some SDK demo need to put the data in the noncache area for the SDRAM, you also can see the original area is indicated to the SDRAM area. So, we need to change it to the internal RAM when you don't use the external SDRAM.

You can try it on your side.

If you still have question about it, please kindly let me know.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for explanation, Kerry

Do you see the same issue in debug mode following the procedure as you showed? the serial handle ends up in ITC memory location 0, and it hangs.

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

You are welcome.

Could you please also share one screenshot about serial handle ends up in ITC memory location 0?

Then, I will test it on my side.

Now, you want to use the ITCM, and it have issues, right? So, you use the DTCM instead of it, right?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Kerry

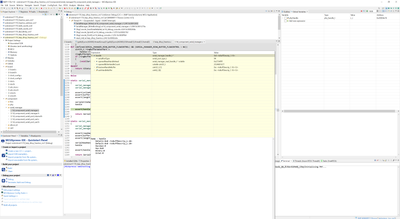

See the screen shot below, the Terminal window prints out Initializing PHY and then hangs at the location shown. If I change the both NonCacheable setting to SRAM_DTC_cm7 in Managed Linker Script , then no this issue, and it works fine, thanks.

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

ITCM for NonCacheable setting also works on my side, please check my test result and the attached demo which I have written for you:

This is my DHCP test result:

You can test it on your MIMXRT1170-EVK board.

Wish it helps you!

BTW, 2024 Chinese Spring Festival: Feb 9th to Feb 18th in total 10 days.

We will in the Spring Festival vacation, and back to work from 2.19th. During this time, you also can create the case, then our Mexico colleague will help you in your new case.

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Kerry

Thanks for trying, I see it works now because you create another section of SRAM_ITC_cm7_usr, which is not located on the memory address 0 location of ITC, otherwise it won't work, I will trying to do same in future if I need to use ITC too.

Happy Chinese New Year!

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1 ,

You are always welcome!

If you don't divide the specific area for your usr data, it may influence the original project requred ITCM area, that's why I define SRAM_ITC_cm7_usr.

If you have any RT issues in the future, welcome to create the new question post to discuss it.

Best Regards,

Kerry