- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX处理器

- :

- i.MX RT Crossover MCUs Knowledge Base

- :

- How to configure LPSPI clock on I.MXRT1050

How to configure LPSPI clock on I.MXRT1050

How to configure LPSPI clock on I.MXRT1050

How to configure LPSPI clock on I.MXRT1050

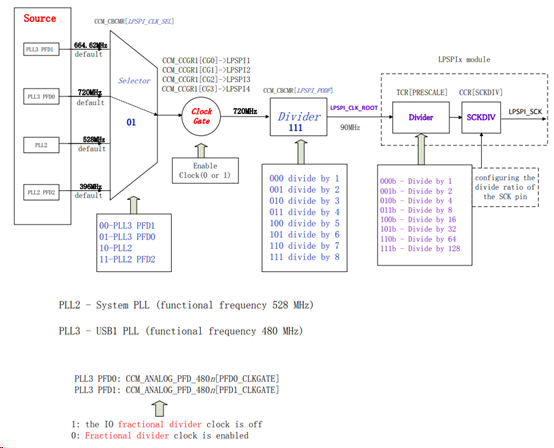

The document will introduce how to configure LPSPI clock on I.MXRT1050. The purpose is to help IMXRT customers better understand the clock tree and configure LPSPI clock in SDK.

Customer can configure LPSPI clock according to the following steps:

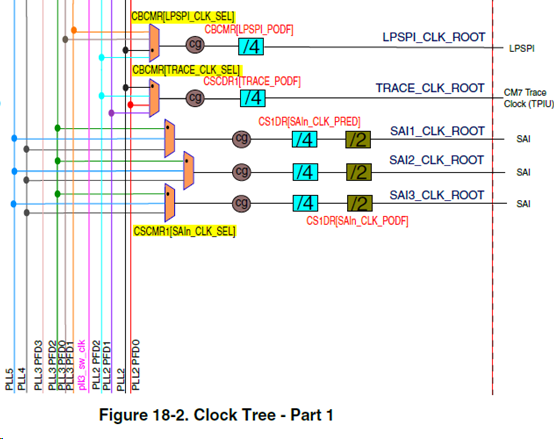

1 Select Source according to the clock tree.

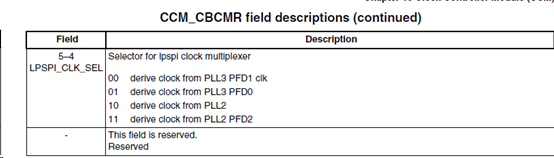

2 Set LPSPI_CKL_SEL according to the register CCM_CBCMR.

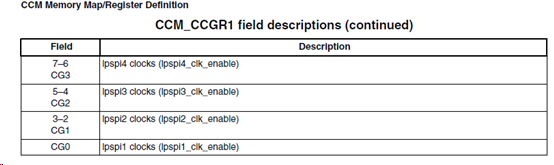

3 Enable LPSPIn clock according to the register CCM_CCGR1.

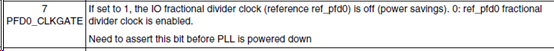

4 Set clock gate according to register CCM_ANALOG_PFD_480n[PFDn_CLKGATE].

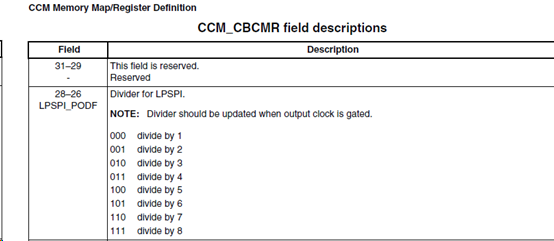

5 Set LPSPI_PODF according to register CCM_CBCMR.

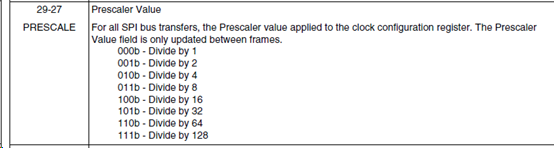

6 Set TCR[PRESCALE] according to LPSPIx module.

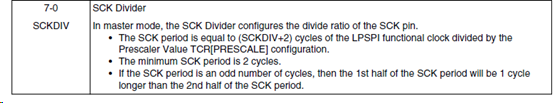

7 Set CCR[SCKDIV] according to LPSPIx module.

The customer can get the value LPSPI_CLK according to the above steps

Hi

See also this document which gives a practical overview of the clock tree: https://www.utasker.com/docs/iMX/i.MX_RT_1021_uTasker.pdf

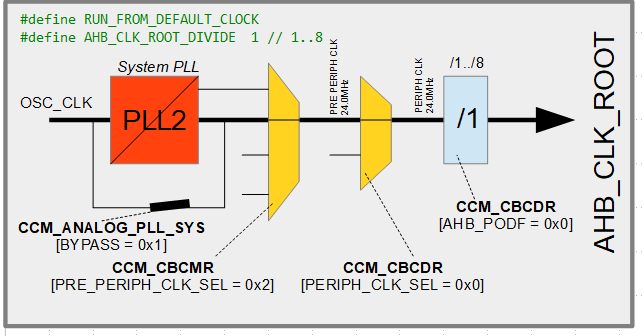

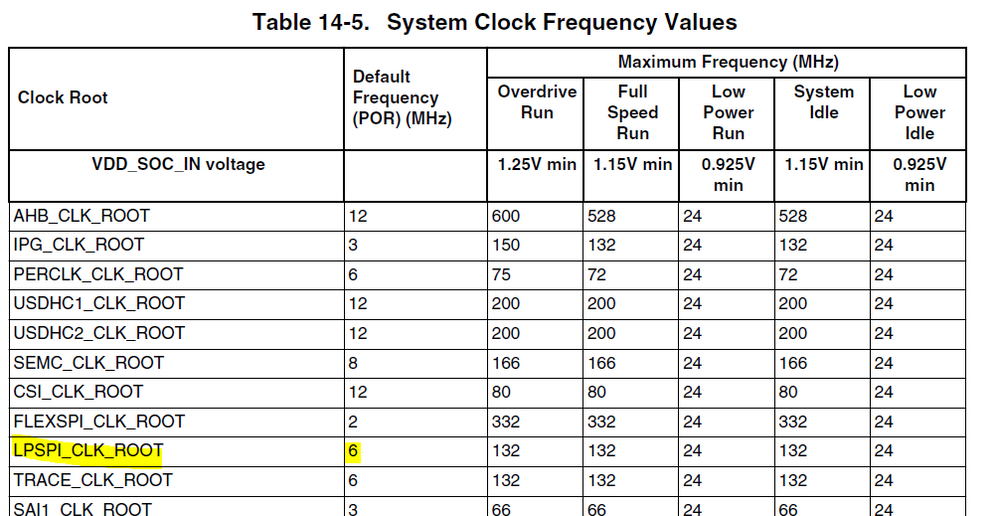

In the case of the LPSPI_CLK_ROOT the default is for the "system" PLL2 to be used as source, divided by 4, which gives a clock speed of 132MHz (the maximum that the LPSPI can use).

However, if the PLL2 is bypassed the speed will be 24MHz/4 (6MHz). The pre-scaler can be adjusted between 1 and 8 to choose the exact frequency that is preferred (3MHz, 3.429MHz, 4MHz, 4.8MHz, 6MHz, 8MHz, 12MHz or 24MHz).

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Thank you Mark, I'm working on RT1052, doesn't it have the same clock tree you attached (rt1021)? According to rt1050RM, LPSPI_CLK_ROOT can only source from PLL2 and PLL3, if the PLL2 is disabled (bypassed), why does it still have a 24MHz? If so, I can put RT1052 work in low power mode and keep LPSPI working at the same time. Thank you again Mark!

Tom

The i.MX RT 1052 has the same clock tree with regard to the LPSPI paths.

The PLL bypass is controlled by the BYPASS bit in the register CCM_ANALOG_PLL_SYS, which is set to '1' after a reset - this is not shown directly in the clock tree diagram in the reference manuals

This is the default state of PLL2: It is off and bypassed, meaning that there is 24MHz at its output.

When it is enabled one first turns on the PLL and waits for it to lock and stabilise, then one removes the bypass so that the output is stable at 528MHz.

Reference code:

_SET_REGISTER(CCM_ANALOG_PFD_528, (CCM_ANALOG_PFD_528_PFD2_CLKGATE | CCM_ANALOG_PFD_528_PFD1_CLKGATE | CCM_ANALOG_PFD_528_PFD0_CLKGATE)); // disable PFD outputs

CCM_ANALOG_PLL_SYS = (CCM_ANALOG_PLL_SYS_POWERUP | CCM_ANALOG_PLL_SYS_ENABLE | CCM_ANALOG_PLL_SYS_BYPASS | CCM_ANALOG_PLL_SYS_DIV_SELECT); // power up the PLL, enable its output but don't yet remove its bypass

CCM_ANALOG_PLL_SYS_NUM = 0; // ensure the fixed frequency (528MHz) is used

_WAIT_REGISTER_FALSE(CCM_ANALOG_PLL_SYS, CCM_ANALOG_PLL_SYS_LOCK); // wait for PLL2 to lock at 528MHz

_CLEAR_REGISTER(CCM_ANALOG_PLL_SYS, CCM_ANALOG_PLL_SYS_BYPASS); // clear the bypass

If LPSPI is clocked from PLL2 (528MHz) initially (divided by 4 to give max. 132MHz) its clock will reduce to 6MHz when the bypass is set and can be increased to 24MHz by then settings its pre-scaler to 1.

To use the 24MHz again one needs to bypass it again (and optionally turn off the PLL), but not before setting the LPSPI pre-scaler back to 4 , to avoid its clock root from being out of specification after PLL2 again at 528MHz.

What I don't know is whether your are switching automatically between the modes or whether you can control the sequences by code during the switching.

Note also that the LPSPI's default is 6MHz, which is explained by the default state discussed above:

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Thanks Mark, you provided so detailed information. Now, I can get it bypassed and 24M OSC works for LPSPI.

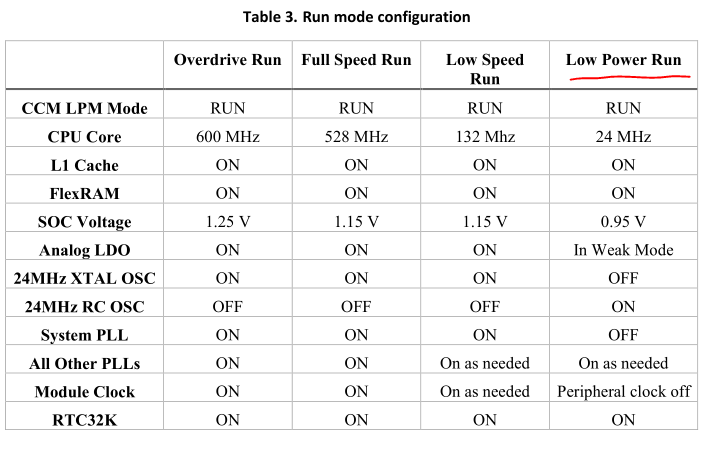

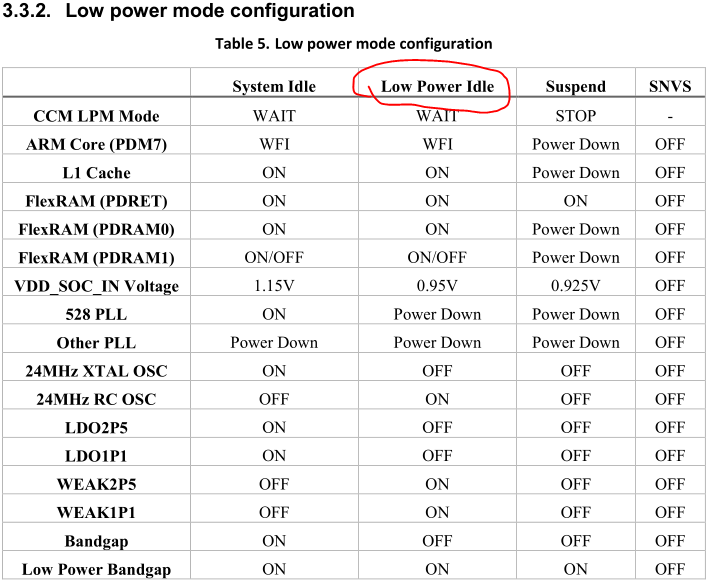

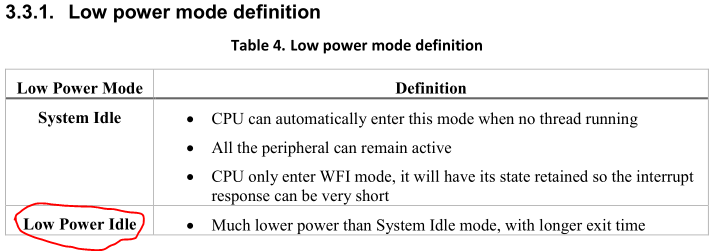

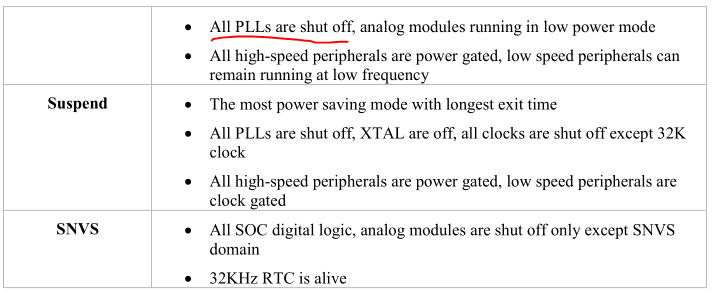

One more question, my system was running in LOW POWER RUN mode but with 24M clock LPSPI, is it possible to make RT1050 go to LOW POWER IDLE mode? The NXP Application Note said all the PLLs should be disabled, does it mean that bypass is not allowed either? Actually, what I want is that RT1050 works in LOW POWER RUN mode normally and goes to LOW POWER IDLE if nothing to do (MCU is in WFI), but if LPSPI is always working (keep PLL2 bypassing), is it able to go to LOW POWER IDLE mode?

Hi Tom

I don't yet have enough experience with the low power modes to be able to give a definitive answer but the bypass works with the PLL disabled so I expect that there will be no problem with this mode.

Regards

Mark

The Data Sheet IMXRT1060CEC, on page 70, Table 57, shows a footnote number 1,

"Absolute maximum frequency of operation (fop) is 30 MHz. The clock driver in the LPSPI module for f_periph must be guaranteed this limit is not exceeded."

There are comments on other forums that the device has been run at 60MHz, and in fact I tried that briefly and it does seem to transfer data ok.

So, why must it be guaranteed that the 30MHz limit is not exceeded?

Are there any other ways to achieve a 60MHz SPI with the i.MX RT 1060 processors? If so, can you please provide a working example.

Thank you