- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

imx8 mipi csi CLK signal with different terminal resistor

Hello,

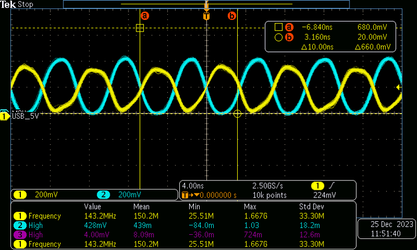

We have two unit, one is okay to capture, and the CLK signal is like "MIPI_CLK1.png". The other one cannot capture image normally with high probability (90%), we measure the CLK signal, the signal looks fine as "MIPI_CLK1.png". After adjusting damping resistor by our HW on the issue unit, it can capture images normally.

Are there any methods about adjusting the IMX8 setting like changing damping resistor?

Environment description: IMX8MP + TP2860 decorder + MIPI CSI + 2 lane

- Signal that cannot capture images before adjusting damping resistor on the issue unit.

- Signal that can capture images after adjusting damping resistor on issue unit, it looks shift but is workable.

HW modification is as below and attached "MIPI_hw_modify.png"

Hi @KenBCHu

The root cause should still be hardware layout.

You can try to adjust HS_RX_ TERMINATION_ IMPEDENCE bit in MIPI_CSIx_DPHY_SLAVE_CTRL_LOW register. This is a software workaround but may not solve this issue very perfectly.

Excuse me

Already referred to

i.MX 8M Plus Hardware Developer Guide, Rev. 0, 03/2021

Table 24. Trace impedance recommendations (continued)

Differential signaling, MIPI (CSI and DSI),

Almost all plagiarized

i.MX 8M Plus LPDDR4 EVK computing module design files

8MPLUSLPD4-CPU/LAY-46368_A1.brd

Waiting for nxp design requirements to design. Is there any important hardware design information or regulations that can be re-evaluated and referred to?

Hi @Zhiming_Liu,

We try to modify three type of MIPI_CSIx_DPHY_SLAVE_CTRL_LOW registers as attached patch, but it seem not work on the issue unit.

By the way, we update the issue situation and we found happened at some units. Please refer to updated post. Any suggestion from your side?

Thanks.

By the way, we update the issue situation and we found happened at some units.

-->Can you evaluate the probability of this issue with the board? Maybe it's a difference caused by the manufacturing process.