- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: imx6 sata eye pattern test

imx6 sata eye pattern test

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI anyone:

My project using imx6q need to do eye pattern test for sata(sata signal test). We are success on 1.5G signal test, because the default signal is 1.5G. When we connect with SATA hardisk, it does generate 3G signal, but after pull out the hardisk, SATA module reset to 1.5G. How to keep it to 3G?

The platform is : yocto , kernel:4.1.15

here is log:

root@imx6qsabresd:~# dmesg | grep ata -i

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] Memory: 698308K/1048576K available (8264K kernel code, 447K rwdata, 3060K rodata, 432K init, 443K bss, 22588K reserved, 327680K cma-reserved, 0K highmem)

.data : 0x80b84000 - 0x80bf3f20 ( 448 kB)

[ 0.217144] libata version 3.00 loaded.

[ 2.151055] ahci-imx 2200000.sata: fsl,transmit-level-mV not specified, using 00000024

[ 2.157721] ahci-imx 2200000.sata: fsl,transmit-boost-mdB not specified, using 00000480

[ 2.164456] ahci-imx 2200000.sata: fsl,transmit-atten-16ths not specified, using 00002000

[ 2.171341] ahci-imx 2200000.sata: fsl,receive-eq-mdB not specified, using 05000000

[ 2.181806] ahci-imx 2200000.sata: SSS flag set, parallel bus scan disabled

[ 2.187532] ahci-imx 2200000.sata: AHCI 0001.0300 32 slots 1 ports 3 Gbps 0x1 impl platform mode

[ 2.195047] ahci-imx 2200000.sata: flags: ncq sntf stag pm led clo only pmp pio slum part ccc apst

[ 2.206753] ata1: SATA max UDMA/133 mmio [mem 0x02200000-0x02203fff] port 0x100 irq 313

[ 2.763434] ata1: SATA link up 3.0 Gbps (SStatus 123 SControl 300)

[ 2.774511] ata1.00: ATA-8: ST95005620AS, SD22, max UDMA/133

[ 2.778947] ata1.00: 976773168 sectors, multi 0: LBA48 NCQ (depth 31/32)

[ 2.789386] ata1.00: configured for UDMA/133

[ 2.813687] scsi 0:0:0:0: Direct-Access ATA ST95005620AS SD22 PQ: 0 ANSI: 5

[ 2.849438] mxc_vdoa 21e4000.vdoa: i.MX Video Data Order Adapter(VDOA) driver probed

[ 6.658768] EXT3-fs (mmcblk2p2): mounted filesystem with ordered data mode

[ 8.777651] FAT-fs (mmcblk2p1): Volume was not properly unmounted. Some data may be corrupt. Please run fsck.

[ 9.162073] FAT-fs (sda1): Volume was not properly unmounted. Some data may be corrupt. Please run fsck.

log when pull out the hardisk:

root@imx6qsabresd:~# ata1: exception Emask 0x10 SAct 0x0 SErr 0x10200 action 0xe frozen

ata1: irq_stat 0x00400000, PHY RDY changed

ata1: SError: { Persist PHYRdyChg }

ata1: hard resetting link

ata1: SATA link down (SStatus 0 SControl 300)

ata1: hard resetting link

ata1: SATA link down (SStatus 0 SControl 300)

ata1: limiting SATA link speed to 1.5 Gbps

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jiang

one can try to change register SATA_P0SCTL field SPD "Speed Allowed" to 3.0 Gb/s

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

while looking for information regarding sata compliance tests, I found your post in the nxp community, which includes some very interesting information in the answers I could use for our tests on our own iMX6Q-board.

The most important question for me is how to configure the sata controller to set it into the respective modes to able to transmit the pattern adjusted in register SATA_BISTCR continuously. Until now I could not finish this task.

Could you please share some information how you configured the test setup on the iMX6Q?

Thank you in advance

Elmar Albert

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

would it be possible for you to share with us the complete SATA test reports - Gen1, Gen2, with PLL6 as refclk and with external clock as refclk?

It would help us with analysis.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Jive:

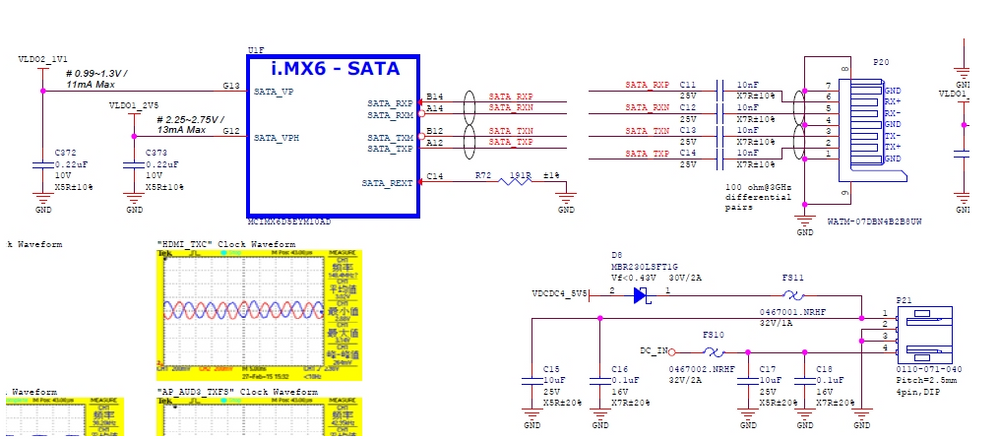

For sata test

It needs to adjust two things:

1:

memtool -32 0x20e0034=0x0593E4FE

set "Transmit level" to 1.240v.

2: use external clock, bypass PLL6

I reference this to set it.

https://community.nxp.com/thread/304283

i.MX6Q: Using an external reference for PCIe

江亚强

软件工程师

Shenzhen Huameishi Technology Co., Ltd

深圳市华美视科技有限公司

深圳市南山区科苑路6号科技园工业大厦东702

Tel:0755-26037882-616

Fax:0775-26037766

Mail:yaqiang.jiang@huameishi.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

thank you very much for a quick response and the reports. Do you also have reports with PLL6 that have failed, so we could compare the overall results and margins?

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

thank you very much for the reports. We appreciate your cooperation.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jiang

one can try to change register SATA_P0SCTL field SPD "Speed Allowed" to 3.0 Gb/s

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igor:

Thanks, it works.

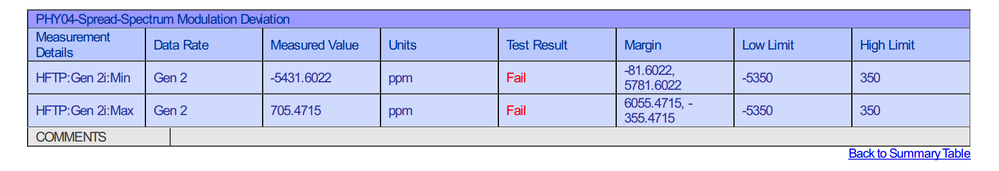

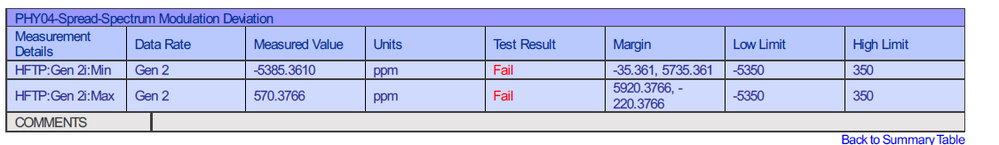

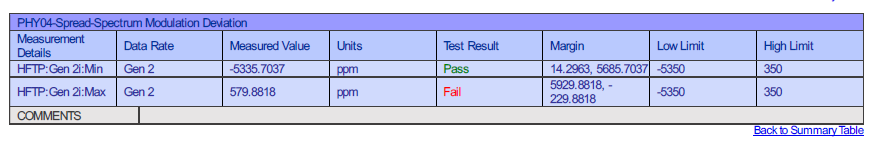

But the test fail on "Spread-Spectrum Modulation Deviation"

what is the possible cause about it ?

The "spreed-spectrum" is enabled in " IOMUXC_GPR13".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jiang,

have you checked whether the reference clock applied to SATA already uses spread spectrum?

If the applied RefClk is already spread spectrum, this bit must be deasserted.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jan:

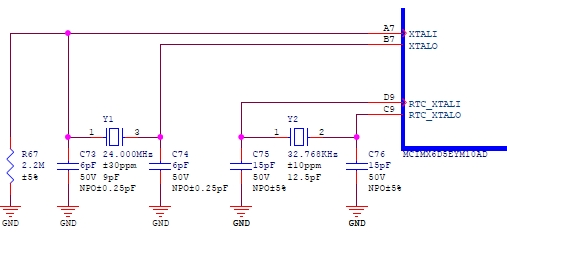

But how to check/set the spreed spectrum of RefClk ?

The sata ref clock is selected from CCM_ANALOG_MISC1n ( 01011 SATA_REF — SATA ref clock

), and it's generated from "Ethernet PLL" 100M. But I can find any register to set the "spreed spectrum".

configure in imx6q.dtsi

sata: sata@02200000 {

compatible = "fsl,imx6q-ahci";

reg = <0x02200000 0x4000>;

interrupts = <0 39 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6QDL_CLK_SATA>,

<&clks IMX6QDL_CLK_SATA_REF_100M>,

<&clks IMX6QDL_CLK_AHB>;

clock-names = "sata", "sata_ref", "ahb";

status = "disabled";

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

1. Do you use our reference board or do you have your own custom board?

In case you have a custom board:

a) Have you refered to our reference boards how the SATA interface is designed?

b) Have you refered to our HWDG, RM and met all the layout criteria (impedance control etc.?)

c) Have you checked whether your crystal selection meets the required PPM for SATA?

On our reference boards we have passed the Gen2 validation, including the Spread Spectrum Deviation test. I am in process of investigating if we used the default ref clock (PLL6 - ENET PLL) for the validation or some else (improbable but to be sure).

2. I did some digging and found another customer who had troubles passing the validation. This worked for them:

Set GPR13 to 0589ACFC (set SATA_PHY_2 to 1.24 V). I suggest you try it.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jan:

2. It does help by set SATA_PHY_2 to 1.24V, but still not pass.

1. it used my own board, it's reference to the " reference board"

The ppm of 24Mhz is 30.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiang,

I now have confirmed that we passed the validation using PLL6 on our reference design.

The schematic looks fine, crystal is precise enough. Is the layout ok?

Use the following recommendations for the SATA.

- SATA differential pairs should have a differential impedance of 100.

- Each differential pair should be length matched to ± 5 mils.

- Follow standard high-speed differential routing rules for signal integrity.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Jan:

Thanks for you support. The test have passed by using external clock as PCIE, bypass PLL6.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiang,

thank you for letting us know. I will investigate this further.

Best Regards,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jan:

I and jiang used the default ref clock (PLL6 - ENET PLL) ,set SATA_PHY_2 to 1.24V,and the layout is ok to test.

“HFTP: Gen 2i:Min” is Pass ,But the “HFTP: Gen 2i:Max” is fail.

PLL6 - ENET PLL and Controls the frequency of the ethernet reference clock vaule is 100MHz

root@imx6qsabresd:~# ./testscript/can/memtool -32 0x20c8160 1

Reading 0x1 count starting at address 0x020C8160

0x020C8160: 8000040B

root@imx6qsabresd:~# ./testscript/can/memtool -32 0x20c80e0 1

Reading 0x1 count starting at address 0x020C80E0

0x020C80E0: 80182002

SATA_PHY_2 value is 1.24V

root@imx6qsabresd:~# ./testscript/can/memtool -32 0x20e0034 1

Reading 0x1 count starting at address 0x020E0034

0x020E0034: 0593E4FE

what is the possible cause about it ?

Best Regards,

Corey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

by the way, the 1.5G sata test passed.