- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: iMX8QM LPDDR4 RPA Support ROW_Addresses == 17 ?

iMX8QM LPDDR4 RPA Support ROW_Addresses == 17 ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a problem with a customized iMX8QM LPDDR4 ( 2 x 4GiB ) memory.

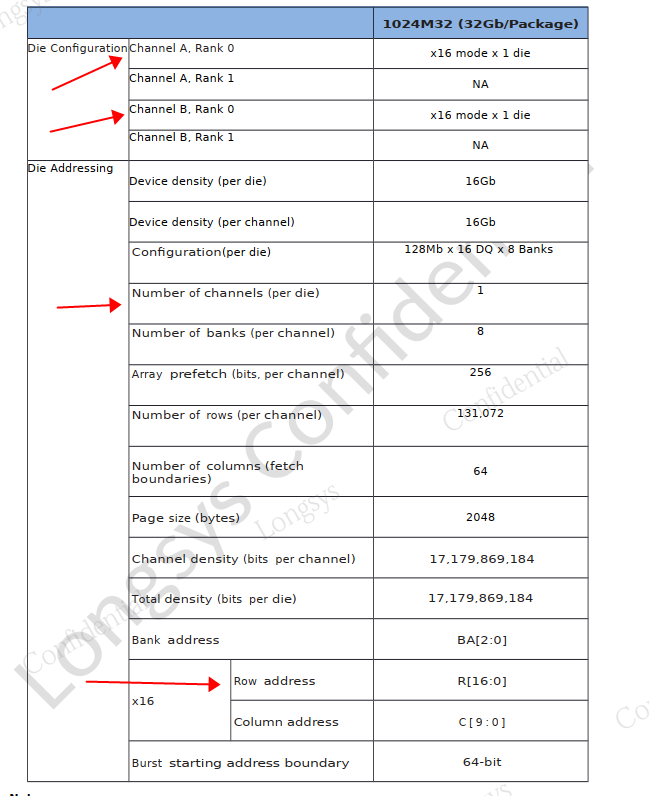

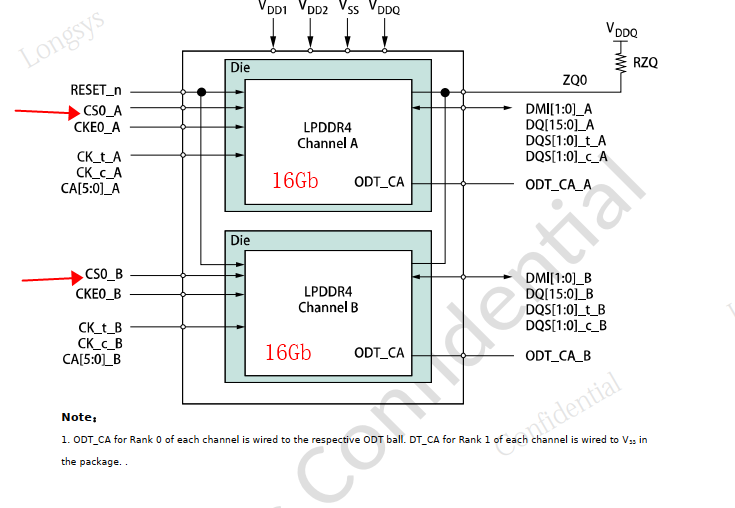

The table below shows memory device configuration. 16Gb per channel,1 Rank per channel .

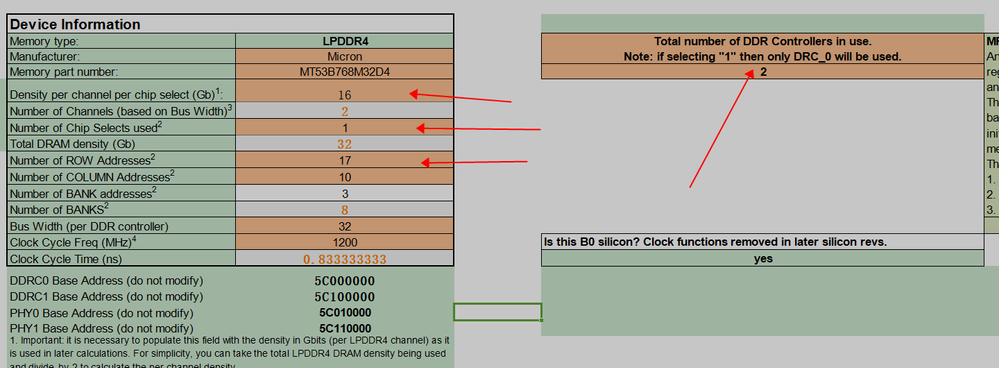

I configed MX8QM_B0_LPDDR4_RPA_1.6GHz_v20.xlsx file like this: Chip Selects used is 1 and Number of Row Addresses is 17.

But it doesn't pass when i use mx8_ddr_stress_test_ER14 DDR Tester tool. Config log seems like ok, but Stress Test Blocking at [ t0.1: data is addr test ]. The log below is all Stress Test log.

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 17, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 2

Density per chip select: 4096MB

Density per controller is: 4096MB

Total density detected on the board is: 8192MB

density assumes all controllers are being used. Adjust the tested

density per your board configuration if not all controllers are used

No DDR data training errors detected for DDRC0

No DDR data training errors detected for DDRC1

============================================

--------------------------------

--Running DDR test on region 1--

--------------------------------

....

t0.2: row hop read test

...

....

t2: byte-wise SSN armv8_x32 test

..

t3: memcpy pseudo random pattern test

....................................................................

t4: IRAM_to_DDRv1 test

...

--------------------------------

--Running DDR test on region2--

--------------------------------

...

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your patience, now SCFW lilmits the DDR size to 6GB both in DDR tool and Linux BSP.

1. Replace mx8qmb0_scfw_download.bin in DDR_tool/bin with the attached binary. You can stress test all 8GB memory size with your DDR script.

2. Modify board_system_config() in board.c in your SCFW project as follows

/* Board has 6GB8GB memory so fragment upper region and retain 4GB */

BRD_ERR(rm_memreg_frag(pt_boot, &mr_temp, 0x980000000ULL, 0xA00000000ULL,

0xFFFFFFFFFULL));

Hope this help you.

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please tell us which version of the SCFW and kernel linux are you using? Just to know if the programing aid that you are using is compatible.

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi israelhernandez

SCFW : imx-scfw-porting-kit-1.5.0

linux kernel version 5.4.24

Android SDK is : imx-android-10.0.0_2.3.0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your patience, now SCFW lilmits the DDR size to 6GB both in DDR tool and Linux BSP.

1. Replace mx8qmb0_scfw_download.bin in DDR_tool/bin with the attached binary. You can stress test all 8GB memory size with your DDR script.

2. Modify board_system_config() in board.c in your SCFW project as follows

/* Board has 6GB8GB memory so fragment upper region and retain 4GB */

BRD_ERR(rm_memreg_frag(pt_boot, &mr_temp, 0x980000000ULL, 0xA00000000ULL,

0xFFFFFFFFFULL));

Hope this help you.

Regards,

Israel H.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Israel H.,

I am using the iMX8M. The LPDDR4 that I am using is 4GB with 1 CS. I want to test the LPDDR4 using the DDR Tool v3.1. I set the density to 32Gb and set the Row to 17. But the DDR Tool still show the Row size is 16. The RPA is v24. Can you provide the firmware that can support the 17 bit row?

Here is the DDR Tool log:

*************************************************************************

MX8 DDR Stress Test V3.10

Built on Feb 5 2020 14:08:44

*************************************************************************

--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x91d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122

- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 800MHz

DDR Clock: 1600MHz

============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 16, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 2048MB

Density per controller is: 2048MB

Total density detected on the board is: 2048MB

============================================

MX8M: Cortex-A53 is found

*************************************************************************

Regards,

Simon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Anyone can help on this issue? I do need this support in order to use LPDDR4 devices with 17 row.

Thanks,

Simon