- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

This is a user problem reading + understanding manual:

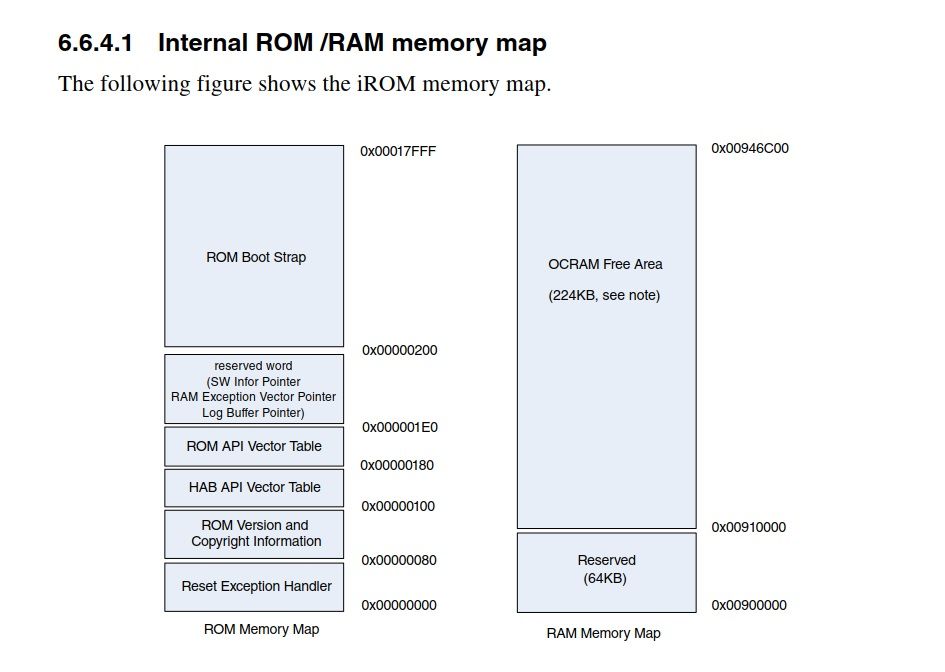

The figure says 224 is free ( = 128(EPDC) + 64(128 - 64res) + 32(PXP) ), and "see note".

In note: "The entire OCRAM region can be used freely post boot. ... "

So can the entire OCRAM 288KB be used freely post boot, or only 224? (I can't say why I can't understand the doc ... ).

And if the 64KB is still reserved, what is it reserved for .. (is it secret :smileyhappy:) ?

已解决! 转到解答。

Hello,

The entire OCRAM 288KB be used freely post boot.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

Hello,

The entire OCRAM 288KB be used freely post boot.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

Hello Yuri!

Do I understand correctly, that I can't use adresses 0x00900000-0x0090ffff for storing my Cortex-M4 firmware because this range is reserved by Linux kernel and is used by it during boot process?

As I see from FreeRTOS linker scripts - they all use 0x00910000 as a start address. I tried to edit default linker script to use first 0x00900000 and then 0x00901000 adresses as a start address along with disabling corresponding ocram entries in the devicetree, but I see that my M4 firmware stops working right after kernel starts booting.

I use imx-5.4.47 kernel

My modifications:

imx7d.dtsi:

ocram: sram@901000 {

compatible = "mmio-sram";

reg = <0x901000 0x1f000>;

clocks = <&clks IMX7D_OCRAM_CLK>;

+ status = "disabled";

};

my devicetree:

reserved-memory {

#address-cells = <1>;

#size-cells = <1>;

ranges;

m4_reserved: m4@0x00901000 {

no-map;

reg = <0x00901000 0x1f000>;

};

};

Did I miss something?

Thanks in advance.