- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX8QXP Cortex M4 caches replacement policy

i.MX8QXP Cortex M4 caches replacement policy

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX8QXP Cortex M4 caches replacement policy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

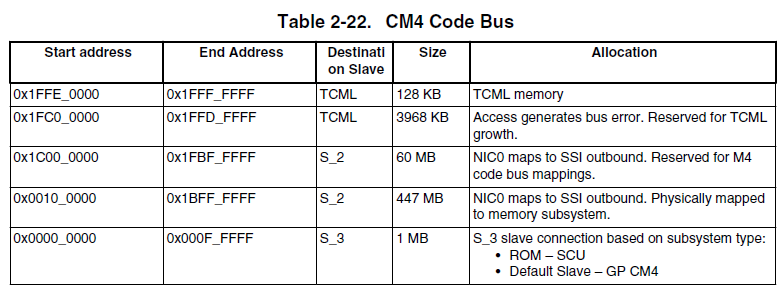

I'm currently working on the cortex M4 in the i.MX8QXP. I want to fill both caches of the M4 (Code and System caches) with dirty entries. Once, I know both caches are filled, I want to measure how long it takes to clean an invalidate both caches. To do so, I need to know the cache replacement policy for both caches. I don't find the information in the IMX8QXP reference manual. Is there an algorithm I can use to fill both caches with dirty entries?

From my understanding from previous discussion on this forum the cache linked to the TCM_L will be kind of hard to fill with dirty entries since the memory map for this region looks like this

Kind Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi david_binet,

The memory attributes of TCM_L address region is hardwired as non-cacheable. This means M core skips cache controller when accessing TCM_L or even TCM_U whenever these regions are configured.

Both of the Code cache and System cache are implemented as below:

- CACHE - 16 KByte size = (256 sets) x (32-byte lines) x (2-way set associative) for both PS and PC cache on CM4.

-

cache line always in 0x20 address alignment (32-byte in one line)

You would see there are two ways for each cache with the total size of 16KB for each cache part.

So I suggest to fill 16KB address continuous data for other memory instead of TCM, for example OCRAM or DDR.

And in theory this will fully fill the cache line with dirty tags if you don't do a cache clean.

Hope it helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

david.binet@ca.thalesgroup.com

Hello,

I am afraid customers can use only C-functions, provided in the SDK in fsl_cache.c (fsl_cache.h)

to control the caches.

Welcome | MCUXpresso SDK Builder

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

The information provided in fsl_cache.c isn't sufficient. From the documentation, I know the L1 data and instruction cache replacement policy of the A35 and also the L2 cache. I'm expecting the same type of information to be provided for both M4 caches.

Kind Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@david_binet

Hello,

"The CM4 subsystem cache uses a single counter to do round robin replacement for the 2-way, set associative cache.

The replacement algorithm is not LRU or round robin by set, it is a single, one bit state for the whole cache."

Regards,

Yuri.