- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello community,

i wanted to know, why are the following power rails shown in the MCIMX6UL-EVK design schematic

VDD_ARM_IN: 400 mA

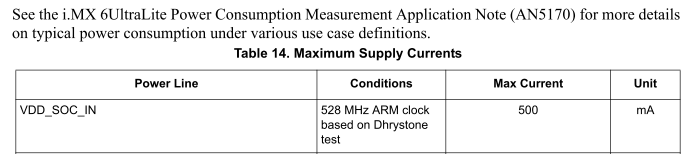

VDD_SOC_IN: 500 mA

Because there is only one power rail and this is VDD_SOC_IN.

Defined with a maximum supply current of 500 mA (i.MX6UL datasheet)

Does it mean the i.MX6UL need more than 500 mA at VDD_SOC_IN - Rail (900 mA given from schmeatic) ?

Best regards

已解决! 转到解答。

Hello Juergen Elst,

The values on the i.MX6UL Datasheet are correct. I would say that the reason why there is more capacity on the schematic is because it’s using LDOs instead of a PMIC so they are listing the capacity of the LDO itself rather than the requirements.

The extra current does not hurt but should not be required.

Regards,

Hello Juergen Elst,

The values on the i.MX6UL Datasheet are correct. I would say that the reason why there is more capacity on the schematic is because it’s using LDOs instead of a PMIC so they are listing the capacity of the LDO itself rather than the requirements.

The extra current does not hurt but should not be required.

Regards,