- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: i.MX6DQ CSI gated mode VSYNC

i.MX6DQ CSI gated mode VSYNC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are trying to support a new camera on CSI0 (parallel sensor interface). Our sensor works in ITU601 mode that looks like the "gated" mode, except that HSYNC is active during the complete duration of an image (starting 16 pixel clock cycles before the first HSYNC gets active, and stopping 16 pixel clock cycles after the last HSYNC gets inactive).

It doesn't match with the normal usage of the gated mode (described at §37.4.3.6.2 of the RM) but should work if the VSYNC is edge-triggered (either on the rising or the falling edge).

If the level of VSYNC is taken into account, it probably won't work.

Has anyone used gated mode with a similar signal VSYNC ?

Is there any internal information on GATED MODE indicating if such a VSYNC signal could also work ?

Thanks for any feedback.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Herve

you are right, VSYNC is edge-triggered and

this is mentioned in sect.4.11.10.2 Sensor Interface Timings

i.MX6DQ Datasheet (rev.4, 7/2015)

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Herve

you are right, VSYNC is edge-triggered and

this is mentioned in sect.4.11.10.2 Sensor Interface Timings

i.MX6DQ Datasheet (rev.4, 7/2015)

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, VSYNC is latched on the rising edge when working in GATED MODE.

§4.11.10.2.2 of http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf seems wrong concerning data sampling : "Data is latched at the rising edge of the valid pixel clocks." Chronogramms clearly show that data sampling occur on the falling edge of the pixel clock.

What are the blanking constraints when working in GATED MODE ?

I didn't find information on this topic in the manuals... To be more precise, this question could be split in several sub-questions :

- When the VSYNC signal rising edge occurs, how many pixel clock cycles [min..max] should we have before asserting HSYNC ?

- At the end of a line, when HSYNC is deasserted, how many pixel clock cycles [min..max] should we have before re-asserting HSYNC ?

- At the end of the last line, when HSYNC is deasserted, how many pixel clock cycles [min..max] should we have before the next rising edge of VSYNC ?

- Do the above "blanking constraints" depend on the resolution, format, or pixel clock frequency ?

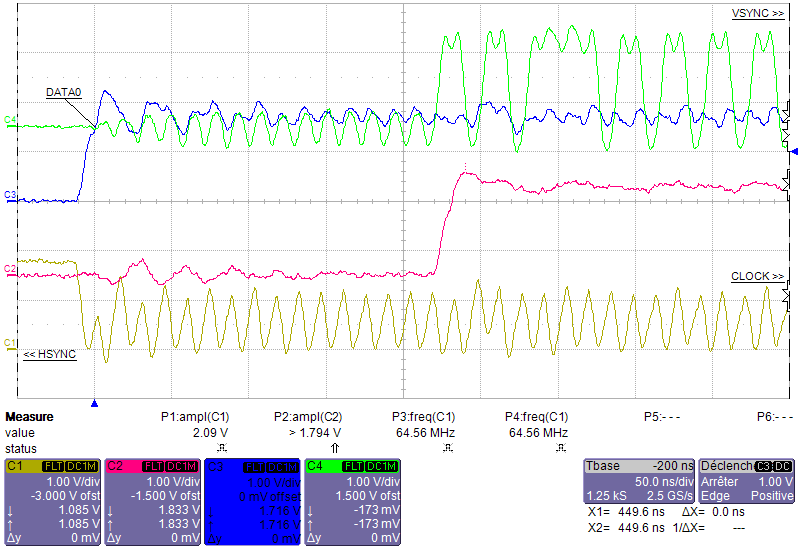

For information, here is a capture of our VSYNC rising edge followed by HSYNC assertion. Signals are a bit noisy due to cables soldered on our PCB. Is there anything wrong explaining why it doesn't work (320x200 in YUV422) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one can look at docx on link below

About HSYNC timing of CSI input in i.MX6DQ.

also had you set correct CSI_DATA_EN as described below

~igor