- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

i.MX6 Solo / LVDS panel artifacts

Using the mainline kernel on i.MX6 Solo with connected LVDS panel, I see artifacts that look like some data lines to the LDB are one pixel clock late. These are especially apparent in horizontal red-to-black and black-to-red gradients, where one can see one pixel wide light or dark vertical stripes in regular intervals, depending on the direction of the gradient.

On one device with a 24-bit SPWG LVDS panel, the artifacts only appear in the red channel, and only when driving the LDB LVDS0 channel from IPU DI0. When switching to IPU DI1, the artifacts disappear completely. The DI pixel clock is synchronized to the LDB_DI clock, which is sourced from PLL5 in each case.

On another device with a 18-bit SPWG LVDS panel, the artifacts are stronger, appear also in the blue and green color channels, and are also visible when switching to DI1. When rendering 1-pixel wide vertical gradients, these don't appear as a straight line, but are shifted or spread over two pixels horizontally, depending on the brightness value. On this hardware, replacing the i.MX6S CPU module with an otherwise identical i.MX6Q CPU gets rid of the artifacts. What could be the cause of this behaviour?

Philipp,

Could this issue be related to this one? Check the "Summary: Recommended Configuration" table.

Regards,

Fabio Estevam

Hi Philipp,

You can also try to invert the DI clock polarity.

Hi,

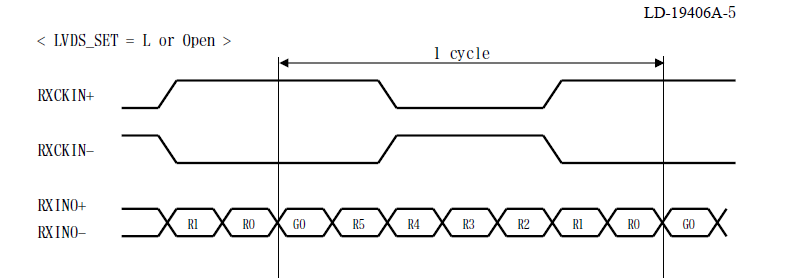

Do you know how to invert LVDS clock polarity? I use IMX6DL, Kernel 3.14.52, uboot 2015.04, my new LCD's LVDS Clock is like follow. I need invert the LVDS clock polarity, But, I don't know how to setting the register.

Hi Leavs,

Unfortunately it's not possible to invert LVDS clock polarity by changing register values. See the following thread:

If you need to invert LVDS clock polarity, have you tried to invert LVDS clock pins?

Yes. I don't know if it works, but was the suggestion made on thread I sent.

Hi Leavs, thanks for opening a new thread. I just answered.

Best regards,

Rogerio

I should have mentioned this was the first thing I tried. That didn't result in any visible changes either.

Hi philippzabel,

I don't know what could be happening. Do you know if it's reproducible on i.MX6 Sabre SD board?

I can try to test it on my board. What kernel and branch have you tested it? Do I need to apply any additional patch?

Rgds

Rogerio

Hi Rogerio,

unfortunately I don't have access to any i.MX6Solo based Sabre board.

I have pushed a test branch with the current state that shows the symptoms on

Phytec PBA-B-01 with i.MX6Solo and EDT ETM0700G0DH6 LVDS panel here:

http://git.pengutronix.de/?p=pza/linux.git;a=shortlog;h=refs/heads/test/pbab01-lvds

regards

Philipp

Hi Philipp,

I tested your kernel on i.MX6DL Sabre SD and I didn't have problems on LVDS display image.

Unfortunately I don't have any i.MX6S with LVDS to test.

I suppose your problem can be related to some wrong display timing setting.

Regards,

Rogerio

Hi Philipp,

I'm building your kernel to test on my board (i.MX6 Sabre SD).

Rgds

Rogerio

This issue seems to be the exactly the one I had some time ago (I'm not sure).

The problem was solved changing the initialization sequence of LDB register, moving it to the end of the initialization sequence.

Original sequence : LDB -> IPU_MUX -> IPU.

Suggest sequence: IPU_MUX -> IPU ->LDB.

Are you able to make some tests based on suggestion above? Please, let me know if you need more details and I can check if I can have more information.

Hi Rogerio,

thanks for the hint, unfortunately that did not help yet. Right now the sequence determined in drm_crtc_helper.c is:

encoder prepare -> crtc prepare -> crtc mode_set -> encoder mode_set -> crtc commit -> encoder commit

The LDB->DI clock parent is set in encoder prepare, then the IPU is enabled in crtc commit (enabling the pixel

clock and the LDB clocks), and LVDS_MUX and LDB are set in encoder commit. That is IPU -> MUX -> LDB.

I have moved the multiplexer setting from encoder commit to encoder mode_set, resulting in MUX -> IPU -> LDB.

I have a board with this problem on the desk ready for further tests.

I'd be happy if you could get more information about this issue.