- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: i.MX6 DDR Stress Test Tool V2.70 calibration fails.

i.MX6 DDR Stress Test Tool V2.70 calibration fails.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang,

We are working our custom board with iMX6 Quad processor. On trying the DDR3 calibration for 1GB with DDR Stress Tool V2.70 using GUI we are getting an error as: ERROR FOUND, we can't get suitable value !!!!

We have been working to resolve this for long time but unsuccessful.

thanks for the help in advance. The log is as below:

Density per chip select: 1024MB

============================================

Current Temperature: 35

============================================

DDR Freq: 396 MHz

ddr_mr1=0x00000004

Start write leveling calibration...

running Write level HW calibration

Write leveling calibration completed, update the following registers in your initialization script

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00150017

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x001F0016

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x00150023

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x00080011

Write DQS delay result:

Write DQS0 delay: 23/256 CK

Write DQS1 delay: 21/256 CK

Write DQS2 delay: 22/256 CK

Write DQS3 delay: 31/256 CK

Write DQS4 delay: 35/256 CK

Write DQS5 delay: 21/256 CK

Write DQS6 delay: 17/256 CK

Write DQS7 delay: 8/256 CK

Starting DQS gating calibration

. HC_DEL=0x00000000 result[00]=0x11011111

. HC_DEL=0x00000001 result[01]=0x11011111

. HC_DEL=0x00000002 result[02]=0x01000010

. HC_DEL=0x00000003 result[03]=0x01000010

. HC_DEL=0x00000004 result[04]=0x11111111

. HC_DEL=0x00000005 result[05]=0x11111111

. HC_DEL=0x00000006 result[06]=0x11111111

. HC_DEL=0x00000007 result[07]=0x11111111

. HC_DEL=0x00000008 result[08]=0x11111111

. HC_DEL=0x00000009 result[09]=0x11111111

. HC_DEL=0x0000000A result[0A]=0x11111111

. HC_DEL=0x0000000B result[0B]=0x11111111

. HC_DEL=0x0000000C result[0C]=0x11111111

. HC_DEL=0x0000000D result[0D]=0x11111111

ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

Error: failed during ddr calibration

It seems from your suggestion that calibration has failed at byte 1 and byte 6.

Can you please suggest any specific issue in the board? And how did you decode the issue is with byte 1 and byte 6?

I also request you to suggest the solution if any.

Thanks and Regards,

Pranav

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pranav,

Please consider Yuri's comments.

Seems you miss one question below.

1. How many boards see this issue?

If you can guarantee design is fine, then we will focus on soldering and DDR device.

In order to reduce effort, let's check low 16bit only.

Suggestions:

1. change a new DDR chip on lowest 16bit.

And using Scritp aid and generate 16 bit script for debug.

https://community.nxp.com/docs/DOC-94917

2. change DDR chip from another vendor.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Problem solved. I have configured a wrong uart.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It is also works well.

Please contact SW expert for your boot issue.

I believe DDR HW related factors had been excluded.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @linwang

The calibration test is successful also stress test is successful. But u-boot is not booting. Please guide if there is any suggestion.

Below is the attached calibration report:

============================================

DDR Stress Test (2.6.0)

Build: Aug 1 2017, 17:33:25

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 Dual/Quad (0x63)

Internal Revision = TO1.2

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000000

SRC_SBMR2(0x020d801c) = 0x20000001

============================================

ARM Clock set to 1GHz

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 14, col size: 10

Chip select CSD0 is used

Density per chip select: 1024MB

============================================

Current Temperature: 35

============================================

DDR Freq: 396 MHz

ddr_mr1=0x00000004

Start write leveling calibration...

running Write level HW calibration

Write leveling calibration completed, update the following registers in your initialization script

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x000F0017

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00180011

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x00100023

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x000B0014

Write DQS delay result:

Write DQS0 delay: 23/256 CK

Write DQS1 delay: 15/256 CK

Write DQS2 delay: 17/256 CK

Write DQS3 delay: 24/256 CK

Write DQS4 delay: 35/256 CK

Write DQS5 delay: 16/256 CK

Write DQS6 delay: 20/256 CK

Write DQS7 delay: 11/256 CK

Starting DQS gating calibration

. HC_DEL=0x00000000 result[00]=0x11111111

. HC_DEL=0x00000001 result[01]=0x11101010

. HC_DEL=0x00000002 result[02]=0x00000000

. HC_DEL=0x00000003 result[03]=0x00000000

. HC_DEL=0x00000004 result[04]=0x11111111

. HC_DEL=0x00000005 result[05]=0x11111111

. HC_DEL=0x00000006 result[06]=0x11111111

. HC_DEL=0x00000007 result[07]=0x11111111

. HC_DEL=0x00000008 result[08]=0x11111111

. HC_DEL=0x00000009 result[09]=0x11111111

. HC_DEL=0x0000000A result[0A]=0x11111111

. HC_DEL=0x0000000B result[0B]=0x11111111

. HC_DEL=0x0000000C result[0C]=0x11111111

. HC_DEL=0x0000000D result[0D]=0x11111111

DQS HC delay value low1 = 0x02010201, high1=0x03030303

DQS HC delay value low2 = 0x02020201, high2=0x03030303

loop ABS offset to get HW_DG_LOW

. ABS_OFFSET=0x00000000 result[00]=0x11111011

. ABS_OFFSET=0x00000004 result[01]=0x11111111

. ABS_OFFSET=0x00000008 result[02]=0x11111111

. ABS_OFFSET=0x0000000C result[03]=0x10111011

. ABS_OFFSET=0x00000010 result[04]=0x10100010

. ABS_OFFSET=0x00000014 result[05]=0x10110011

. ABS_OFFSET=0x00000018 result[06]=0x10110011

. ABS_OFFSET=0x0000001C result[07]=0x00110010

. ABS_OFFSET=0x00000020 result[08]=0x00100010

. ABS_OFFSET=0x00000024 result[09]=0x00000000

. ABS_OFFSET=0x00000028 result[0A]=0x00000000

. ABS_OFFSET=0x0000002C result[0B]=0x00000000

. ABS_OFFSET=0x00000030 result[0C]=0x00000000

. ABS_OFFSET=0x00000034 result[0D]=0x00000000

. ABS_OFFSET=0x00000038 result[0E]=0x00000000

. ABS_OFFSET=0x0000003C result[0F]=0x00000000

. ABS_OFFSET=0x00000040 result[10]=0x00000000

. ABS_OFFSET=0x00000044 result[11]=0x00000000

. ABS_OFFSET=0x00000048 result[12]=0x00000000

. ABS_OFFSET=0x0000004C result[13]=0x00000000

. ABS_OFFSET=0x00000050 result[14]=0x00000000

. ABS_OFFSET=0x00000054 result[15]=0x00000000

. ABS_OFFSET=0x00000058 result[16]=0x00000000

. ABS_OFFSET=0x0000005C result[17]=0x00000000

. ABS_OFFSET=0x00000060 result[18]=0x00000000

. ABS_OFFSET=0x00000064 result[19]=0x00000000

. ABS_OFFSET=0x00000068 result[1A]=0x00000000

. ABS_OFFSET=0x0000006C result[1B]=0x00000000

. ABS_OFFSET=0x00000070 result[1C]=0x00000000

. ABS_OFFSET=0x00000074 result[1D]=0x00000000

. ABS_OFFSET=0x00000078 result[1E]=0x00000000

. ABS_OFFSET=0x0000007C result[1F]=0x00000000

loop ABS offset to get HW_DG_HIGH

. ABS_OFFSET=0x00000000 result[00]=0x00000000

. ABS_OFFSET=0x00000004 result[01]=0x00000000

. ABS_OFFSET=0x00000008 result[02]=0x00000000

. ABS_OFFSET=0x0000000C result[03]=0x00000000

. ABS_OFFSET=0x00000010 result[04]=0x00000000

. ABS_OFFSET=0x00000014 result[05]=0x00000000

. ABS_OFFSET=0x00000018 result[06]=0x00000000

. ABS_OFFSET=0x0000001C result[07]=0x00000000

. ABS_OFFSET=0x00000020 result[08]=0x00000000

. ABS_OFFSET=0x00000024 result[09]=0x00000000

. ABS_OFFSET=0x00000028 result[0A]=0x00000000

. ABS_OFFSET=0x0000002C result[0B]=0x00000000

. ABS_OFFSET=0x00000030 result[0C]=0x01000000

. ABS_OFFSET=0x00000034 result[0D]=0x01000000

. ABS_OFFSET=0x00000038 result[0E]=0x01000000

. ABS_OFFSET=0x0000003C result[0F]=0x01000000

. ABS_OFFSET=0x00000040 result[10]=0x01000000

. ABS_OFFSET=0x00000044 result[11]=0x01000100

. ABS_OFFSET=0x00000048 result[12]=0x11001100

. ABS_OFFSET=0x0000004C result[13]=0x11001110

. ABS_OFFSET=0x00000050 result[14]=0x11101110

. ABS_OFFSET=0x00000054 result[15]=0x11101111

. ABS_OFFSET=0x00000058 result[16]=0x11101111

. ABS_OFFSET=0x0000005C result[17]=0x11111111

. ABS_OFFSET=0x00000060 result[18]=0x11111111

. ABS_OFFSET=0x00000064 result[19]=0x11111111

. ABS_OFFSET=0x00000068 result[1A]=0x11111111

. ABS_OFFSET=0x0000006C result[1B]=0x11111111

. ABS_OFFSET=0x00000070 result[1C]=0x11111111

. ABS_OFFSET=0x00000074 result[1D]=0x11111111

. ABS_OFFSET=0x00000078 result[1E]=0x11111111

. ABS_OFFSET=0x0000007C result[1F]=0x11111111

BYTE 0:

Start: HC=0x00 ABS=0x1C

End: HC=0x03 ABS=0x50

Mean: HC=0x01 ABS=0x75

End-0.5*tCK: HC=0x02 ABS=0x50

Final: HC=0x02 ABS=0x50

BYTE 1:

Start: HC=0x01 ABS=0x24

End: HC=0x03 ABS=0x48

Mean: HC=0x02 ABS=0x36

End-0.5*tCK: HC=0x02 ABS=0x48

Final: HC=0x02 ABS=0x48

BYTE 2:

Start: HC=0x00 ABS=0x0C

End: HC=0x03 ABS=0x40

Mean: HC=0x01 ABS=0x65

End-0.5*tCK: HC=0x02 ABS=0x40

Final: HC=0x02 ABS=0x40

BYTE 3:

Start: HC=0x01 ABS=0x10

End: HC=0x03 ABS=0x44

Mean: HC=0x02 ABS=0x2A

End-0.5*tCK: HC=0x02 ABS=0x44

Final: HC=0x02 ABS=0x44

BYTE 4:

Start: HC=0x00 ABS=0x20

End: HC=0x03 ABS=0x58

Mean: HC=0x01 ABS=0x7B

End-0.5*tCK: HC=0x02 ABS=0x58

Final: HC=0x02 ABS=0x58

BYTE 5:

Start: HC=0x01 ABS=0x24

End: HC=0x03 ABS=0x4C

Mean: HC=0x02 ABS=0x38

End-0.5*tCK: HC=0x02 ABS=0x4C

Final: HC=0x02 ABS=0x4C

BYTE 6:

Start: HC=0x01 ABS=0x0C

End: HC=0x03 ABS=0x2C

Mean: HC=0x02 ABS=0x1C

End-0.5*tCK: HC=0x02 ABS=0x2C

Final: HC=0x02 ABS=0x2C

BYTE 7:

Start: HC=0x01 ABS=0x1C

End: HC=0x03 ABS=0x44

Mean: HC=0x02 ABS=0x30

End-0.5*tCK: HC=0x02 ABS=0x44

Final: HC=0x02 ABS=0x44

DQS calibration MMDC0 MPDGCTRL0 = 0x42480250, MPDGCTRL1 = 0x02440240

DQS calibration MMDC1 MPDGCTRL0 = 0x424C0258, MPDGCTRL1 = 0x0244022C

Note: Array result[] holds the DRAM test result of each byte.

0: test pass. 1: test fail

4 bits respresent the result of 1 byte.

result 00000001:byte 0 fail.

result 00000011:byte 0, 1 fail.

Starting Read calibration...

ABS_OFFSET=0x00000000 result[00]=0x11111111

ABS_OFFSET=0x04040404 result[01]=0x11111111

ABS_OFFSET=0x08080808 result[02]=0x11011001

ABS_OFFSET=0x0C0C0C0C result[03]=0x01011000

ABS_OFFSET=0x10101010 result[04]=0x00011000

ABS_OFFSET=0x14141414 result[05]=0x00000000

ABS_OFFSET=0x18181818 result[06]=0x00000000

ABS_OFFSET=0x1C1C1C1C result[07]=0x00000000

ABS_OFFSET=0x20202020 result[08]=0x00000000

ABS_OFFSET=0x24242424 result[09]=0x00000000

ABS_OFFSET=0x28282828 result[0A]=0x00000000

ABS_OFFSET=0x2C2C2C2C result[0B]=0x00000000

ABS_OFFSET=0x30303030 result[0C]=0x00000000

ABS_OFFSET=0x34343434 result[0D]=0x00000000

ABS_OFFSET=0x38383838 result[0E]=0x00000000

ABS_OFFSET=0x3C3C3C3C result[0F]=0x00000000

ABS_OFFSET=0x40404040 result[10]=0x00000000

ABS_OFFSET=0x44444444 result[11]=0x00000000

ABS_OFFSET=0x48484848 result[12]=0x00000000

ABS_OFFSET=0x4C4C4C4C result[13]=0x00000000

ABS_OFFSET=0x50505050 result[14]=0x00000000

ABS_OFFSET=0x54545454 result[15]=0x00000000

ABS_OFFSET=0x58585858 result[16]=0x00000000

ABS_OFFSET=0x5C5C5C5C result[17]=0x00000000

ABS_OFFSET=0x60606060 result[18]=0x00100000

ABS_OFFSET=0x64646464 result[19]=0x00100100

ABS_OFFSET=0x68686868 result[1A]=0x11100111

ABS_OFFSET=0x6C6C6C6C result[1B]=0x11101111

ABS_OFFSET=0x70707070 result[1C]=0x11111111

ABS_OFFSET=0x74747474 result[1D]=0x11111111

ABS_OFFSET=0x78787878 result[1E]=0x11111111

ABS_OFFSET=0x7C7C7C7C result[1F]=0x11111111

Byte 0: (0x0c - 0x64), middle value:0x38

Byte 1: (0x08 - 0x64), middle value:0x36

Byte 2: (0x08 - 0x60), middle value:0x34

Byte 3: (0x14 - 0x68), middle value:0x3e

Byte 4: (0x14 - 0x6c), middle value:0x40

Byte 5: (0x08 - 0x5c), middle value:0x32

Byte 6: (0x10 - 0x64), middle value:0x3a

Byte 7: (0x0c - 0x64), middle value:0x38

MMDC0 MPRDDLCTL = 0x3E343638, MMDC1 MPRDDLCTL = 0x383A3240

Starting Write calibration...

ABS_OFFSET=0x00000000 result[00]=0x10111111

ABS_OFFSET=0x04040404 result[01]=0x10111111

ABS_OFFSET=0x08080808 result[02]=0x10110110

ABS_OFFSET=0x0C0C0C0C result[03]=0x10100010

ABS_OFFSET=0x10101010 result[04]=0x10100010

ABS_OFFSET=0x14141414 result[05]=0x00000000

ABS_OFFSET=0x18181818 result[06]=0x00000000

ABS_OFFSET=0x1C1C1C1C result[07]=0x00000000

ABS_OFFSET=0x20202020 result[08]=0x00000000

ABS_OFFSET=0x24242424 result[09]=0x00000000

ABS_OFFSET=0x28282828 result[0A]=0x00000000

ABS_OFFSET=0x2C2C2C2C result[0B]=0x00000000

ABS_OFFSET=0x30303030 result[0C]=0x00000000

ABS_OFFSET=0x34343434 result[0D]=0x00000000

ABS_OFFSET=0x38383838 result[0E]=0x00000000

ABS_OFFSET=0x3C3C3C3C result[0F]=0x00000000

ABS_OFFSET=0x40404040 result[10]=0x00000000

ABS_OFFSET=0x44444444 result[11]=0x00000000

ABS_OFFSET=0x48484848 result[12]=0x00000000

ABS_OFFSET=0x4C4C4C4C result[13]=0x00000000

ABS_OFFSET=0x50505050 result[14]=0x00000000

ABS_OFFSET=0x54545454 result[15]=0x00000000

ABS_OFFSET=0x58585858 result[16]=0x00000000

ABS_OFFSET=0x5C5C5C5C result[17]=0x00000000

ABS_OFFSET=0x60606060 result[18]=0x00000000

ABS_OFFSET=0x64646464 result[19]=0x00000000

ABS_OFFSET=0x68686868 result[1A]=0x01000000

ABS_OFFSET=0x6C6C6C6C result[1B]=0x01000000

ABS_OFFSET=0x70707070 result[1C]=0x01001100

ABS_OFFSET=0x74747474 result[1D]=0x01001100

ABS_OFFSET=0x78787878 result[1E]=0x11011111

ABS_OFFSET=0x7C7C7C7C result[1F]=0x11111111

Byte 0: (0x08 - 0x74), middle value:0x3e

Byte 1: (0x14 - 0x74), middle value:0x44

(0x0c - 0x74), middle value:0x40Byte 5: (0x14 - 0x78), middle value:0x46

Byte 6: (0x00 - 0x64), middle value:0x32

Byte 7: (0x14 - 0x74), middle value:0x44

MMDC0 MPWRDLCTL = 0x3A3C443E,MMDC1 MPWRDLCTL = 0x44324640

MMDC registers updated from calibration

Write leveling calibration

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x000F0017

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00180011

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x00100023

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x000B0014

Read DQS Gating calibration

MPDGCTRL0 PHY0 (0x021b083c) = 0x42480250

MPDGCTRL1 PHY0 (0x021b0840) = 0x02440240

MPDGCTRL0 PHY1 (0x021b483c) = 0x424C0258

MPDGCTRL1 PHY1 (0x021b4840) = 0x0244022C

Read calibration

MPRDDLCTL PHY0 (0x021b0848) = 0x3E343638

MPRDDLCTL PHY1 (0x021b4848) = 0x383A3240

Write calibration

MPWRDLCTL PHY0 (0x021b0850) = 0x3A3C443E

MPWRDLCTL PHY1 (0x021b4850) = 0x44324640

Success: DDR calibration completed!!!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The calibration looks fine.

What about stress test by this tool?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang

Below is the result of stress test result:

============================================

DDR Stress Test (2.6.0)

Build: Aug 1 2017, 17:33:25

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 Dual/Quad (0x63)

Internal Revision = TO1.2

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000000

SRC_SBMR2(0x020d801c) = 0x20000001

============================================

ARM Clock set to 1GHz

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 14, col size: 10

Chip select CSD0 is used

Density per chip select: 1024MB

============================================

DDR Stress Test Iteration 1

Current Temperature: 40

============================================

DDR Freq: 396 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 413 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 432 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 452 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 475 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 500 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

DDR Freq: 528 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

t1: memcpy8 SSN x64 test

t2: byte-wise SSN x64 test

t3: memcpy11 random pattern test

t4: IRAM_to_DDRv2 test

t5: IRAM_to_DDRv1 test

t6: read noise walking ones and zeros test

Success: DDR Stress test completed!!!

But still my u-boot is not booting. I am getting jump to address message, but there are no messages on the console. any suggestions?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang,

I understand that termination won't help for the delay. I have configured MMDC0_MDMISC = 0x000117C0 to compensate the delay. But still byte 1 is not successful.

Is there any other way to rectify the issue?

Thank you in advance.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pranav,

Two suggestions for lowest 16 bit bus:

1. Do SI siumlation to check your PCB layout.

2. Do compliance test and see if there are some SI issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang

In the Stress Test Tool for my iMX6DQ board minimum frequency that I can set is 300MHz. Also I tried with 528MHz. The result are as follows:

DDR Freq: 528 MHz

ddr_mr1=0x00000004

Start write leveling calibration...

running Write level HW calibration

Write leveling calibration completed, update the following registers in your initialization script

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x0029002D

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00360029

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x0026003A

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x00170024

Write DQS delay result:

Write DQS0 delay: 45/256 CK

Write DQS1 delay: 41/256 CK

Write DQS2 delay: 41/256 CK

Write DQS3 delay: 54/256 CK

Write DQS4 delay: 58/256 CK

Write DQS5 delay: 38/256 CK

Write DQS6 delay: 36/256 CK

Write DQS7 delay: 23/256 CK

Starting DQS gating calibration

. HC_DEL=0x00000000 result[00]=0x11111111

. HC_DEL=0x00000001 result[01]=0x11011111

. HC_DEL=0x00000002 result[02]=0x10010011

. HC_DEL=0x00000003 result[03]=0x00000010

. HC_DEL=0x00000004 result[04]=0x00000010

. HC_DEL=0x00000005 result[05]=0x11111111

. HC_DEL=0x00000006 result[06]=0x11111111

. HC_DEL=0x00000007 result[07]=0x11111111

. HC_DEL=0x00000008 result[08]=0x11111111

. HC_DEL=0x00000009 result[09]=0x11111111

. HC_DEL=0x0000000A result[0A]=0x11111111

. HC_DEL=0x0000000B result[0B]=0x11111111

. HC_DEL=0x0000000C result[0C]=0x11111111

. HC_DEL=0x0000000D result[0D]=0x11111111

ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

Error: failed during ddr calibration

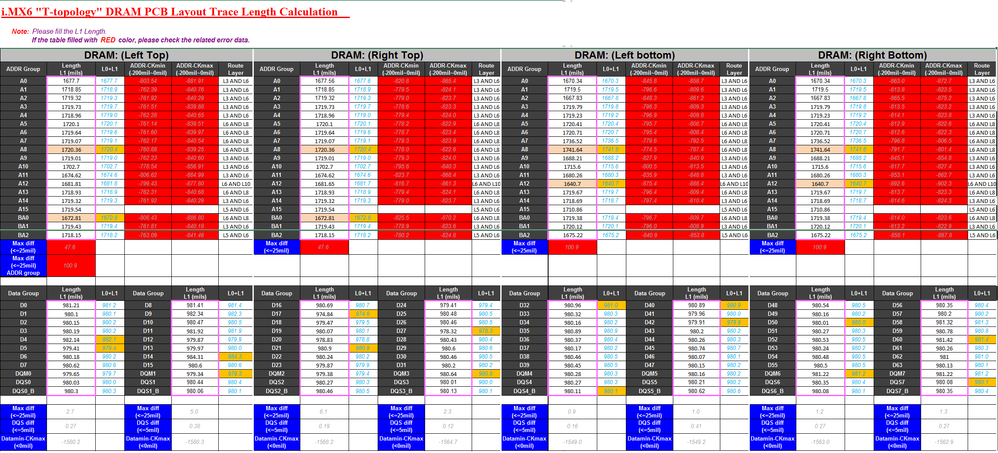

Also I have attached images of my Design checklist Layout details. I see many issues with address and command lengths so I have used a termination IC with 50 ohms pullup for it. I wish you could highlight most critical ones that may cause the issue.

Thanks,

Pranav

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pranav,

Please consider Yuri's comments.

Seems you miss one question below.

1. How many boards see this issue?

If you can guarantee design is fine, then we will focus on soldering and DDR device.

In order to reduce effort, let's check low 16bit only.

Suggestions:

1. change a new DDR chip on lowest 16bit.

And using Scritp aid and generate 16 bit script for debug.

https://community.nxp.com/docs/DOC-94917

2. change DDR chip from another vendor.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang,

I tested the new card and calibration got succeeded. It was the BGA soldering issue.

But still the processor is not booting the u-boot. Loading the u-boot is successful but I am not getting any data on uart-0.

Any suggestions?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please addached calibration report for reference.

What about DDR test at working frequency?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI LinWang,

Currently I am working with only one board. In my Design I had a provision for Termination Regulator for DDR. Scince my clock signal length is 2559.61 mils (> 2250) I populated the Regulator with 50 ohms pull-up to VTT. Now I am getting the following result:

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 14, col size: 10

Chip select CSD0 is used

Density per chip select: 1024MB

============================================

Current Temperature: 32

============================================

DDR Freq: 297 MHz

ddr_mr1=0x00000004

Start write leveling calibration...

running Write level HW calibration

Write leveling calibration completed, update the following registers in your initialization script

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00110012

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x00170010

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x0010001B

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x00070010

Write DQS delay result:

Write DQS0 delay: 18/256 CK

Write DQS1 delay: 17/256 CK

Write DQS2 delay: 16/256 CK

Write DQS3 delay: 23/256 CK

Write DQS4 delay: 27/256 CK

Write DQS5 delay: 16/256 CK

Write DQS6 delay: 16/256 CK

Write DQS7 delay: 7/256 CK

Starting DQS gating calibration

. HC_DEL=0x00000000 result[00]=0x11011111

. HC_DEL=0x00000001 result[01]=0x00000010

. HC_DEL=0x00000002 result[02]=0x00000010

. HC_DEL=0x00000003 result[03]=0x00000010

. HC_DEL=0x00000004 result[04]=0x11111111

. HC_DEL=0x00000005 result[05]=0x11111111

. HC_DEL=0x00000006 result[06]=0x11111111

. HC_DEL=0x00000007 result[07]=0x11111111

. HC_DEL=0x00000008 result[08]=0x11111111

. HC_DEL=0x00000009 result[09]=0x11111111

. HC_DEL=0x0000000A result[0A]=0x11111111

. HC_DEL=0x0000000B result[0B]=0x11111111

. HC_DEL=0x0000000C result[0C]=0x11111111

. HC_DEL=0x0000000D result[0D]=0x11111111

ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

Error: failed during ddr calibration

Also there is one more query. I am trying to access the DDR memory from Read/Write part in the tool. I am able to write and Read the address space properly. Following is the log for the same.

addr=0x10000000,data=0x12345678

Success to write address 0x10000000

addr=0x10000004,data=0x1234ABCD

Success to write address 0x10000004

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x10000000: 0x12345678

memory read is done

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x10000004: 0x1234ABCD

memory read is done

addr=0x10000008,data=0xFFFF0F0F

Success to write address 0x10000008

addr=0x1000000C,data=0x05050F0F

Success to write address 0x1000000c

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x10000008: 0xFFFF0F0F

memory read is done

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x1000000C: 0x05050F0F

memory read is done

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pranav,

According follwing log, "0" means calibration pass, "1" means fail.

Lower bit start from byte0, so byte1 and byte6 can't pass DQS gating calibration.

. HC_DEL=0x00000001 result[01]=0x11011111

. HC_DEL=0x00000002 result[02]=0x01000010

. HC_DEL=0x00000003 result[03]=0x01000010

. HC_DEL=0x00000004 result[04]=0x11111111

Please check these two byte in your design.

Need more info to analysis the issue.

1. How many boards see this issue?

2. Is this the design reviewed by NXP?

3. Comapre with reference design what's the changes? Both schmatic and layout.

4. What's the DDR part number?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi LinWang,

My design is similar to SABER Lite Board.

As per this reference there is no change in the schematic and design uses T-topology for DDR routing.

My DDR part number is AS4C128M16D3-12BAN.

And my design has not been reviewed by NXP.

Also please suggest if there is any solution to resolve Byte 1 and Byte 6 issue.