- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

how to use ldb/lvds in android8 of imx8mq ?

Hi anyone:

Is there any document about how to use lvds in android8 of imx8mq platform ?

Best Regards.

Hi, Jiang:

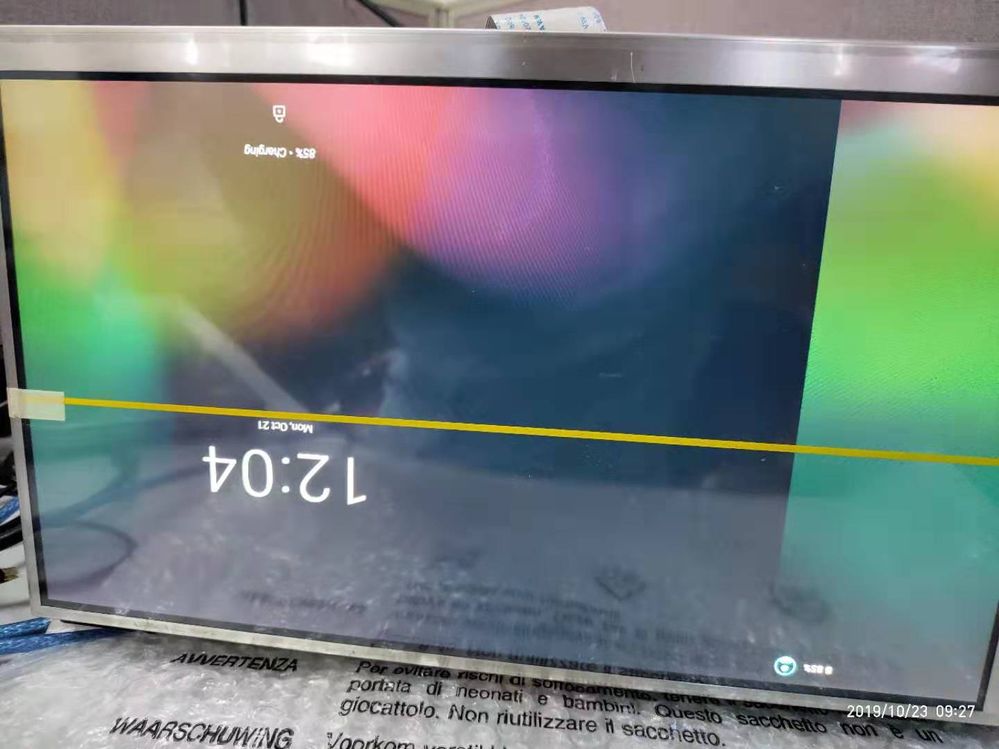

Thank you for your sn65dsi84 's code . I have used it and the LCD(1920X1080) can show . but met some questions, please see the attched file, 1.) the screen shift to right 2.) the colors have distortion.

Can you give me some advice?

thanks.

13534273512

Thomas He.

HI:

does you use external clock or dsi clock for sn65dsi clock input ?

江亚强

软件工程师

Shenzhen Huameishi Technology Co., Ltd

深圳市华美视科技有限公司

深圳市南山区科苑路6号科技园工业大厦605

Tel:0755-26037882-616

Mail:yaqiang.jiang@huameishi.com

HI Hank wang:

Thanks.

but in sn65dsi84 datasheet , when use dsi clock as input , the dsi clock must be set as continuous.

BTW: have you try other lcd resolution ?

datasheet:

8.3.1 Clock Configurations and Multipliers

The LVDS clock may be derived from the DSI channel A clock, or from an external reference clock source. When

the MIPI D-PHY channel A HS clock is used as the LVDS clock source, the D-PHY clock lane must operate in

HS free-running (continuous) mode; this feature eliminates the requirement for an external reference clock

reducing system costs

HI Jiang:

Follow your offered sn65dsi85 driver, I can dispaly 800x600@60Hz while use sn65dsi84 for mipi conver lvds, but encounter an "no singal" tips on another LCD with 1920x1080 resolution, when set CCSR 0x3c as 0x10, I can got the test pattern, could you remind me what's wrong in the process。

BTW,use the same dts and kernel, I do the blowing test:

1) test pattern with single lvds chanel mode on a 800x600 lcd -- ok

2) mipidsi show image to lvds single lvds chanel mode on 800x600 lcd -ok

3) test pattern with dual lvds chanel mode on a 1920x1080 lcd -- ok

4) test pattern witch dual lvds chanel mode (forced in 800x600@60hz) on the 1920x1080 lcd -ok

5) mipi dsi show image to lvds with dual lvds chanel mode (forced in 800x600@60hz) fail, but while connect the 800x600 resolution lcd in one lvds channel, i got the image.

Thanks.

Hi Frank,

I'm also trying to enable sn65dsi84 on our custom board, we use a 1024*600 LVDS panel.

However, the DSI driver can't work out the CM/CN/CO values for D-PHY ref_clk.

Could you share your dts file and timing table of the panel?

imx_nwl_try_phy_speed (583): bit_clk = 403200000 ; pixclock = 50400000

nwl_dsi-imx mipi_dsi@30A00000: [drm:imx_nwl_try_phy_speed] *ERROR* Cannot setup PHY for mode: 1024x600 @50400 kHz

nwl_dsi-imx mipi_dsi@30A00000: [drm:imx_nwl_try_phy_speed] *ERROR* PHY_REF clk: 27000000, bit clk: 403200000

Thanks a lot.

HI :

you can turn up the frequency.

For 1024*600 LVDS, I success in kernel 4.9 but fail in 4.14.

江亚强

软件工程师

Shenzhen Huameishi Technology Co., Ltd

深圳市华美视科技有限公司

深圳市南山区科苑路6号科技园工业大厦605

Tel:0755-26037882-616

Mail:yaqiang.jiang@huameishi.com

Hi Jiang,

I'm trying to add sn65dsi84 to my kernel but I have some trouble with device tree, it is possible to have your entire dts? I'm not very skilled in this stuff yet and I guess I'm making mny errors.

Let me know,

Thanks

HI Lee:

Most likely it's the display_timing problem.

江亚强

软件工程师

Shenzhen Huameishi Technology Co., Ltd

深圳市华美视科技有限公司

深圳市南山区科苑路6号科技园工业大厦605

Tel:0755-26037882-616

Mail:yaqiang.jiang@huameishi.com

Hi Jiang:

Thanks for your share! I added the panel-sn65dsix.c and panel-dsi85.h into my ststem, and I encountered such a problem,the dmesg indicated that

the mipi_dsi_bridge can't find the i2c client device sn65dsi8x.

I added some log massages and then i find that the sn65dsi8x client_dev->dev.driver = NULL. Is the sn65dsi8x need a i2c device driver?, Have you encountered this problem?

My kernel log:

[ 1.052093] [drm] Initialized

[ 1.061372] [drm] Supports vblank timestamp caching Rev 2 (21.10.2013).

[ 1.068015] [drm] No driver support for vblank timestamp query.

[ 1.074129] imx-drm display-subsystem: bound imx-dcss-crtc.0 (ops dcss_crtc_ops)

[ 1.081637] nwl_dsi-imx mipi_dsi@30A00000: Using DCSS as input source

[ 1.088478] panel-ti-sn65dsi8x 30a00000.mipi_dsi_bridge.0: failed to find client platform device

[ 1.097285] panel-ti-sn65dsi8x 30a00000.mipi_dsi_bridge.0: Yao-log:client_dev->dev.driver == NULL!!!

[ 1.106541] nwl-mipi-dsi 30a00000.mipi_dsi_bridge: [drm:nwl_dsi_host_attach] lanes=4, format=0x0 flags=0x813

[ 1.116450] imx-drm display-subsystem: bound mipi_dsi@30A00000 (ops imx_nwl_dsi_component_ops)

[ 1.129560] [drm] OPIPE_CFG: gamut = 3, nl = 1, pr = 1, pix_format = 875713089

[ 1.655077] function:sn65_panel_enable line:1044 -----------

[ 1.721128] Console: switching to colour frame buffer device 240x67

[ 1.783389] imx-drm display-subsystem: fb0: frame buffer device

Thanks & Best Regards

Hi Jiang,

Thanks for the reply. In my case I'm using SN65DSI84 as bridge and auo t21hvn01 for panel. Can you share your changes in fsl-imx8mq-com.dts & fsl-imx8mq-com.dtsi files?

Can I ask you what panel you have used? If the panel is not similar, I guess I need to write drm brdge driver for panel-simple.c

In my so far combinations I couldn't see DSI clock.

Venkatesh

HI :

As attachment.

Hope it can help for you.

BTW, some clock doesn't support by imx8mq, you can higher it up a little.

江亚强

软件工程师

Shenzhen Huameishi Technology Co., Ltd

深圳市华美视科技有限公司

深圳市南山区科苑路6号科技园工业大厦605

Tel:0755-26037882-616

Mail:yaqiang.jiang@huameishi.com