- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Why imx6solo can not boot from nand flash?

HI,

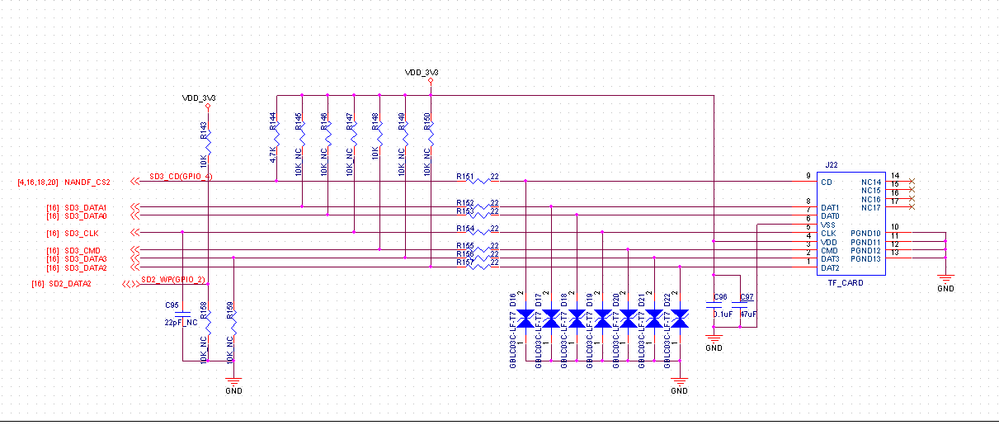

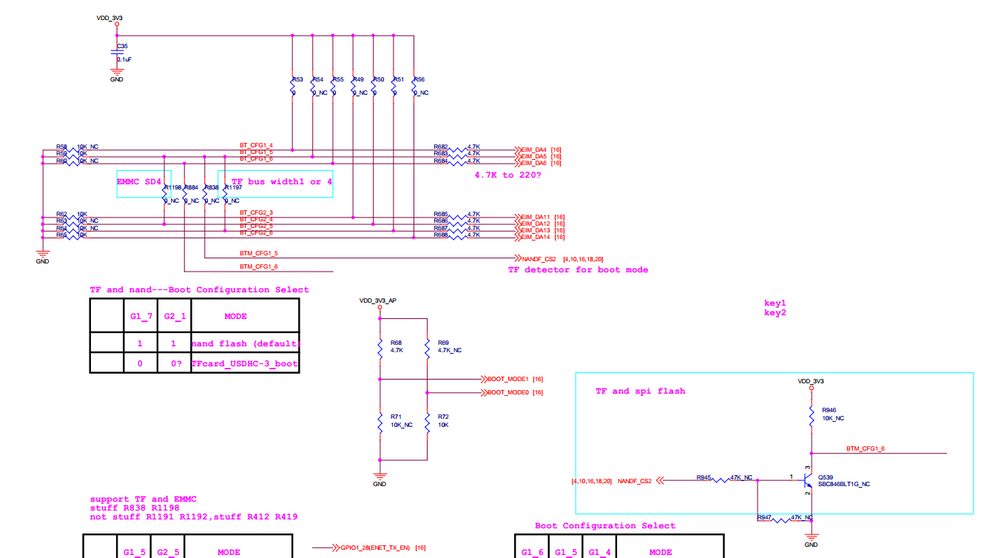

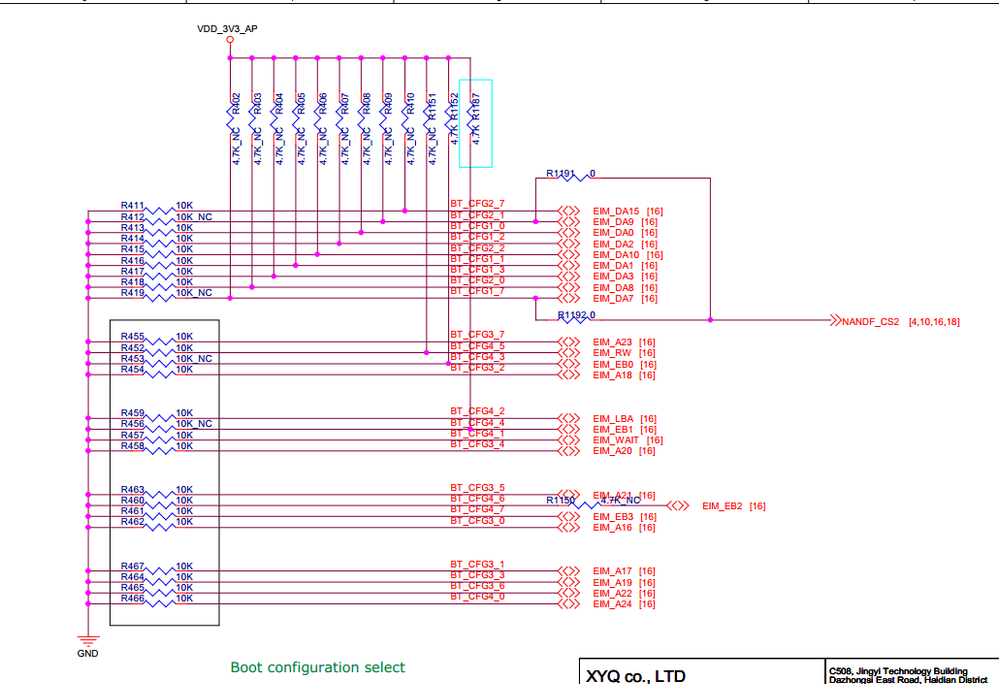

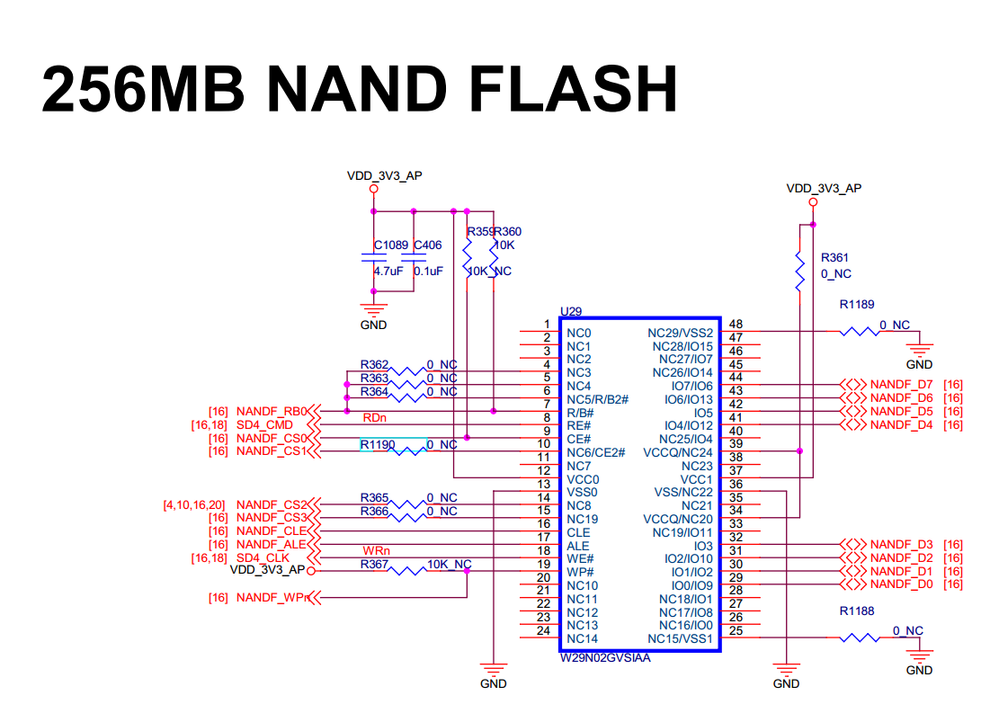

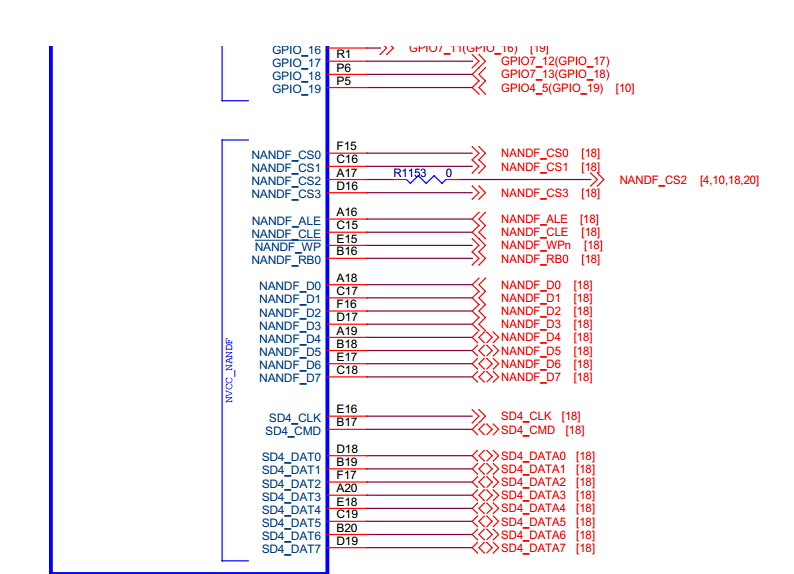

My board can not boot from 256MB nand flash when power on,and nand flash can run when boot from TF cards then manual command to run nand falsh.It looks like that the boot mode is somewhere wrong.The nand is W29N02GVSIAA.The following picture is my sch. and NC means not stuff.

The "NANDF_CS2" connects to TF card socket's CD pin to detect card insert,when insert TFcard,it boot from TF,when not insert TF card,it boot from nand flash.

Hi 翔李

what is full processor name used in the case ?

Best regards

igor

the part number is MCIMX6S6AVM08AC,the picture is following. also show the log of boot information from TF and tf manual command nand run.

hi

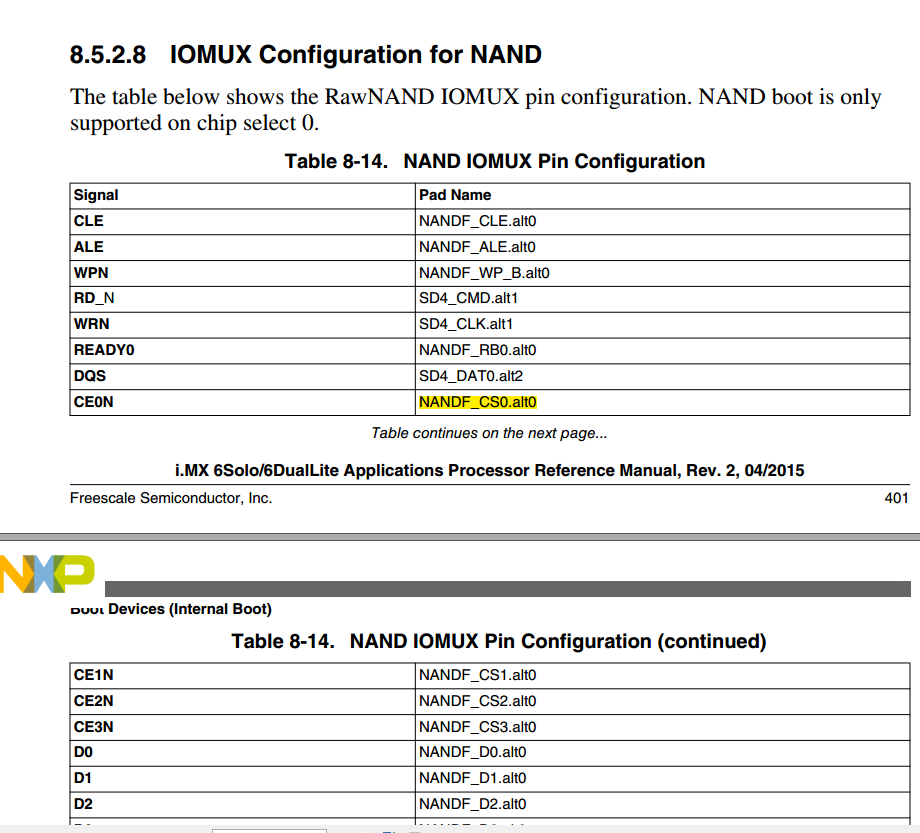

please refer to sect.8.5.2.8 IOMUX Configuration for NAND i.MX6SDL Reference Manual

http://www.nxp.com/assets/documents/data/en/reference-manuals/IMX6SDLRM.pdf

NAND boot is only supported on chip select 0.

general steps for debugging nand boot are given in

https://community.freescale.com/thread/307723

igor

Hi

please try to program nand using mfg tools found on link

i.MX 6 / i.MX 7 Series Software and Development Tool|NXP

use mfgtool2-yocto-mx-sabresd-nand.vbs script

~igor

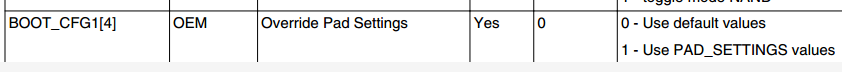

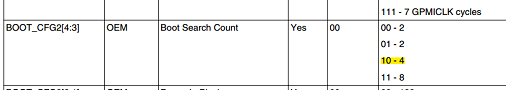

cfg1_4 controls pad settings (affect drive strength and associated with them

signal integrity) defined in Table 5-7. NAND Boot Fusemap i.MX6SDL Reference Manual.

Thanks.

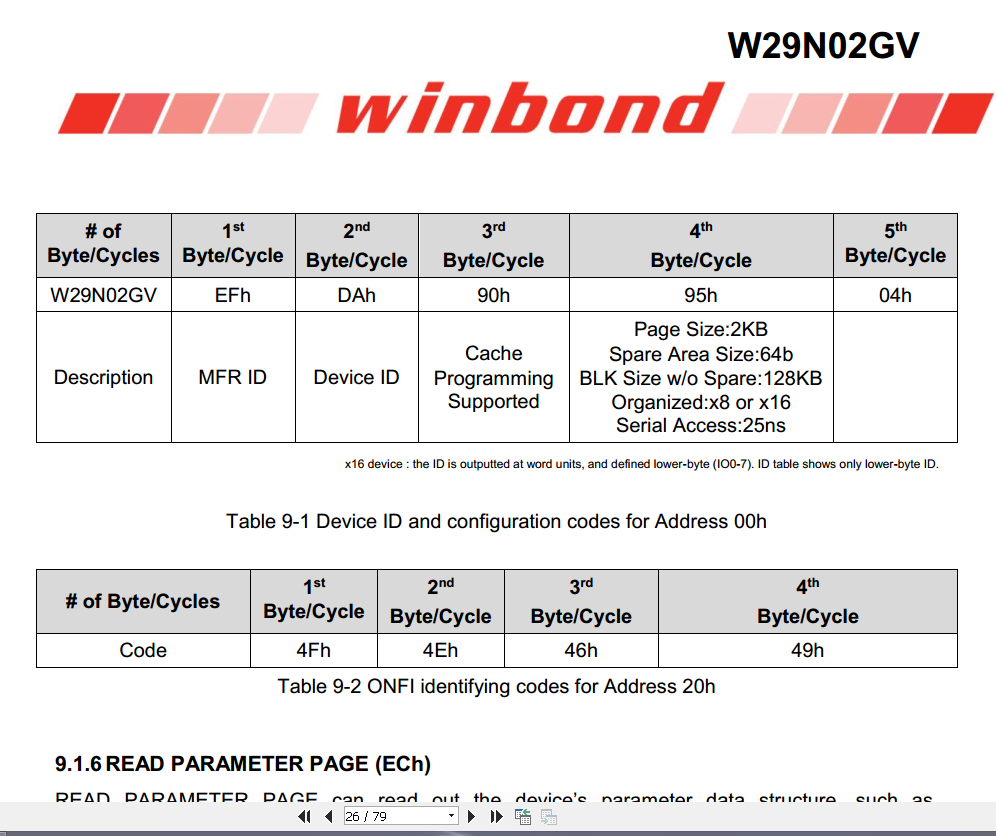

Now I can boot from nand flash when power up,imx6solo can read out the MFR ID and Device ID,but then fail to read ONFI ID(the read result is same as the MFR ID and device ID).why?My nand flash is W29N02GVSIAA.

can you give me the demo software of nand flash?

Log of boot information is following.

Is a u-boot SPL fault. There's a NAND protocol violation in mxs_nand_command() which lead to failure on some NAND devices (like Winbond one) but that still works on some other devices (e.g. Spansion one) that seems to answer anyway.

Here is a patch that solve this issue as can be applied on current u-boot master (this is the patch I've sent mainline)

From d6227c8badce7ce4fa2aad0976a916a6c09c6b1f Mon Sep 17 00:00:00 2001

From: Andrea Scian <andrea.scian@dave.eu>

Date: Tue, 29 Jan 2019 11:30:12 +0100

Subject: [PATCH 1/2] mtd: mxs_nand_spl: fix nand_command protocol violation

mxs_nand_command() implementation assume that it's working with a

LP NAND, which is a common case nowadays and thus uses two bytes

for column address.

However this is wrong for NAND_CMD_READID and NAND_CMD_PARAM, which

expects only one byte of column address, even for LP NANDs.

This leads to ONFI detection problem with some NAND manufacturer (like

Winbond) but not with others (like Samsung and Spansion)

We fix this with a simple workaround to avoid the 2nd byte column address

for those two commands.

Also align the code with nand_base to support 16 bit devices.

Tested on an iMX6SX device with:

* Winbond W29N04GVSIAA

* Spansion S34ML04G100TF100

* Samsung K9F4G08U00

Signed-off-by: Andrea Scian <andrea.scian@dave.eu>

CC: Stefano Babic <sbabic@denx.de>

---

drivers/mtd/nand/raw/mxs_nand_spl.c | 14 +++++++++++++-

1 file changed, 13 insertions(+), 1 deletion(-)

diff --git a/drivers/mtd/nand/raw/mxs_nand_spl.c b/drivers/mtd/nand/raw/mxs_nand_spl.c

index 2d7bbe83cc..ad3b7ade64 100644

--- a/drivers/mtd/nand/raw/mxs_nand_spl.c

+++ b/drivers/mtd/nand/raw/mxs_nand_spl.c

@@ -22,8 +22,20 @@ static void mxs_nand_command(struct mtd_info *mtd, unsigned int command,

/* Serially input address */

if (column != -1) {

+ /* Adjust columns for 16 bit buswidth */

+ if (chip->options & NAND_BUSWIDTH_16 &&

+ !nand_opcode_8bits(command))

+ column >>= 1;

chip->cmd_ctrl(mtd, column, NAND_ALE);

- chip->cmd_ctrl(mtd, column >> 8, NAND_ALE);

+

+ /*

+ * Assume LP NAND here, so use two bytes column address

+ * but not for CMD_READID and CMD_PARAM, which require

+ * only one byte column address

+ */

+ if (command != NAND_CMD_READID &&

+ command != NAND_CMD_PARAM)

+ chip->cmd_ctrl(mtd, column >> 8, NAND_ALE);

}

if (page_addr != -1) {

chip->cmd_ctrl(mtd, page_addr, NAND_ALE);

--

2.19.2

please check Demo Images for sabre ai board, it supports nand.

Best regards

igor