- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

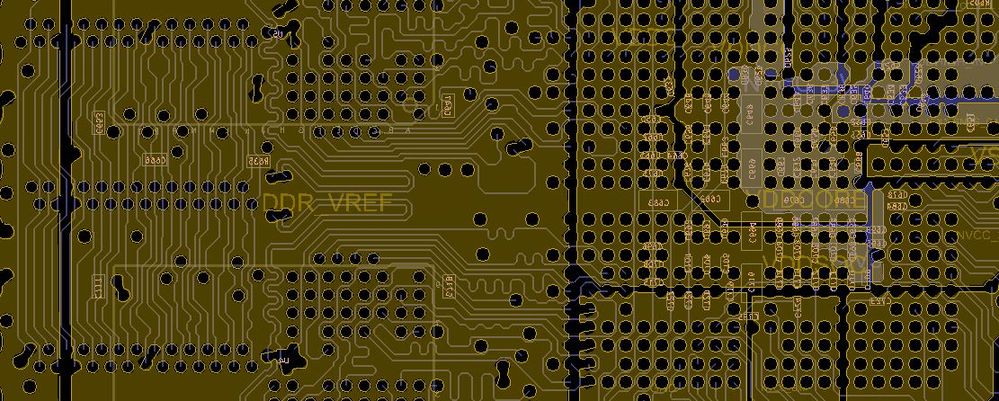

According i.MX6 SMART DEVICE SYSTEM layout board, it uses 8 layers, my question is about the inner layers, they are striplines with a continuos GND plane in one side but in the other side they have a power layer that is broken A LOT of times (they make a lot of power islands), and some important signals cross those broken planes and that would mean a difference in Zo of the line, which mean reflections, so te integrity of the signal won't be optimal and when we are talking about RAM data lines and other kind of sensitive lines that's a big problem, so that thats my question, i mean that's the reference design, but in my opinion is against all theory, can some one tell me if i'm wrong or gimme an awnser to orientate me in this matter please.

This is a screenshot of the internal layer 2 and the power plane, there you can see the SoC and the RAM lines.

已解决! 转到解答。

Hi Javier

yes you are right, reference design may not always

follow User Guide layout recommendations.

Reason is that reference design is developed on very

early stage, when not all specs/datasheet parameters are formalized.

Also reference design tries to put on board as many capabilities as possible,

sacrificing layout theory.

For customers it is recommended to follow i.MX6 User Guide layout recommendations.

Best regards

chip

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Javier

yes you are right, reference design may not always

follow User Guide layout recommendations.

Reason is that reference design is developed on very

early stage, when not all specs/datasheet parameters are formalized.

Also reference design tries to put on board as many capabilities as possible,

sacrificing layout theory.

For customers it is recommended to follow i.MX6 User Guide layout recommendations.

Best regards

chip

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------