- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- QTMR PWM Example

QTMR PWM Example

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

QTMR PWM Example

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MCUXpresso IDE v11.4.1 [Build 6260] [2021-09-15]

SDK_2.x_MIMXRT1160-EVK: Version 2.1.0

EVK1160 PCB

I am trying to get my PWM started using QTIMER2_TIMER0 for GPIO_DISP_B1_01 (D13). Here is my code setup from the driver example:

int main(void)

{

uint8_t i = 0;

qtmr_config_t qtmrConfig;

/* Board pin, clock, debug console init */

BOARD_ConfigMPU();

BOARD_InitPins();

BOARD_BootClockRUN();

BOARD_InitDebugConsole();

/*!

* brief Sets up Quad timer module for PWM signal output.

*

* The function initializes the timer module according to the parameters passed in by the user. The

* function also sets up the value compare registers to match the PWM signal requirements.

*

* param base Quad Timer peripheral base address

* param channel Quad Timer channel number

* param pwmFreqHz PWM signal frequency in Hz

* param dutyCyclePercent PWM pulse width, value should be between 0 to 100

* 0=inactive signal(0% duty cycle)...

* 100=active signal (100% duty cycle)

* param outputPolarity true: invert polarity of the output signal, false: no inversion

* param srcClock_Hz Main counter clock in Hz.

*

* return Returns an error if there was error setting up the signal.

*/

status_t QTMR_SetupPwm(TMR_Type *base,

qtmr_channel_selection_t channel,

uint32_t pwmFreqHz,

uint8_t dutyCyclePercent,

bool outputPolarity,

uint32_t srcClock_Hz)

{

uint32_t periodCount, highCount, lowCount;

uint16_t reg;

status_t status;

if (dutyCyclePercent <= 100U)

{

/* Set OFLAG pin for output mode and force out a low on the pin */

base->CHANNEL[channel].SCTRL |= (TMR_SCTRL_FORCE_MASK | TMR_SCTRL_OEN_MASK);

/* Counter values to generate a PWM signal */

periodCount = srcClock_Hz / pwmFreqHz;

highCount = periodCount * dutyCyclePercent / 100U;

lowCount = periodCount - highCount;

if (highCount > 0U)

{

highCount -= 1U;

}

if (lowCount > 0U)

{

lowCount -= 1U;

}

/* This should not be a 16-bit overflow value. If it is, change to a larger divider for clock source. */

assert(highCount <= 0xFFFFU);

assert(lowCount <= 0xFFFFU);

/* Setup the compare registers for PWM output */

base->CHANNEL[channel].COMP1 = (uint16_t)lowCount;

base->CHANNEL[channel].COMP2 = (uint16_t)highCount;

/* Setup the pre-load registers for PWM output */

base->CHANNEL[channel].CMPLD1 = (uint16_t)lowCount;

base->CHANNEL[channel].CMPLD2 = (uint16_t)highCount;

reg = base->CHANNEL[channel].CSCTRL;

/* Setup the compare load control for COMP1 and COMP2.

* Load COMP1 when CSCTRL[TCF2] is asserted, load COMP2 when CSCTRL[TCF1] is asserted

*/

reg &= (uint16_t)(~(TMR_CSCTRL_CL1_MASK | TMR_CSCTRL_CL2_MASK));

reg |= (TMR_CSCTRL_CL1(kQTMR_LoadOnComp2) | TMR_CSCTRL_CL2(kQTMR_LoadOnComp1));

base->CHANNEL[channel].CSCTRL = reg;

if (outputPolarity)

{

/* Invert the polarity */

base->CHANNEL[channel].SCTRL |= TMR_SCTRL_OPS_MASK;

}

else

{

/* True polarity, no inversion */

base->CHANNEL[channel].SCTRL &= ~(uint16_t)TMR_SCTRL_OPS_MASK;

}

reg = base->CHANNEL[channel].CTRL;

reg &= ~(uint16_t)TMR_CTRL_OUTMODE_MASK;

/* Count until compare value is reached and re-initialize the counter, toggle OFLAG output

* using alternating compare register

*/

reg |= (TMR_CTRL_LENGTH_MASK | TMR_CTRL_OUTMODE(kQTMR_ToggleOnAltCompareReg));

base->CHANNEL[channel].CTRL = reg;

status = kStatus_Success;

}

else

{

/* Invalid dutycycle */

status = kStatus_Fail;

}

return status;

}

}

My question is for this enum:

status_t QTMR_SetupPwm(TMR_Type *base,

qtmr_channel_selection_t channel,

uint32_t pwmFreqHz,

uint8_t dutyCyclePercent,

bool outputPolarity,

uint32_t srcClock_Hz)

Where should these parameters be defined? Are they only initialized or do they have a default value somewhere that I am missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @DFaulkner ,

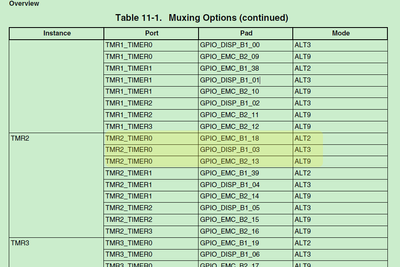

Not all the pins can be used as the QTIMER2_TIMER0 PWM pin, please check the IO chapter:

When you select the related pin, you also need to configure it in the pin_mux.c, please check the current SDK code for QTIMER.

SDK_2_11_0_MIMXRT1160-EVK\boards\evkmimxrt1160\driver_examples\qtmr

Wish it helps you!

Best Regards,

Kerry