- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- PCIe Bandwidth

PCIe Bandwidth

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PCIe Bandwidth

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What bandwidth should we expect to achieve with the I.MX8 PCI-E Gen 2 interface?

Currently, we have a Xilinx Kintex-7 FPGA design and can achieve 2.8 Gbps when transmitting from the I.MX8 to the FPGA and only 2.2 Gbps when receiving from the FPGA to the I.MX8. To achieve the 2.8 Gbps trasmitting rate from the I.MX8 to the FPGA we are using the I.MX8’s PCIe DMA engine.

We would like to achieve above 2.5 Gbps when receiving from the FPGA to the I.MX8. We have tried using the I.MX8’s PCIe DMA engine as well as a DMA engine inside the FPGA with no success. In addition, we have tried pushing test data over the PCIe bus and still the I.MX8 would not accept data faster than 2.2 Gbps.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The data look promising, but I agree with @adamdgray , it lacks some details :

- Hadware : how was made the connection between the boards ? A cable (which one?) between the M2 slots or a cable/card between the B2B connectors ?

- Software : is it possible to have the BSP used for these tests ?

Best regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Regarding to the PCIe protocol, EP is act as bus master to kick off the data transactions.

RC can't act the master in the EP's data transactions.

Hope the information is helpful to you.

Have a nice day!

B.R,

weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Do you have any data for the Root Complex transactions?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No, We don't have the benchmark of the RC transactions.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Adam,

The data is from design team, test diagram is below:

i.MX boar PCIe(RC) <------>i.MX board PCIe(EP)

Hope the information is helpful to you.

Have a nice day!

B.R,

Weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry, that diagram did not provide any new information.

I am asking you to clarify who was the bus master in the data you provided and if you have any information why the data rate is so much slower in one direction.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Adam,

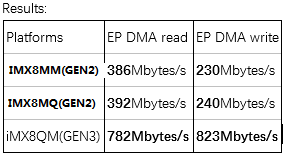

Below is our test result for I.MX8 PCIe:

Two boards, one board PCIe used as EP, the other one PCIe used as RC.

Connect by two board.

Hope the information is helpful to you.

Have a nice day!

B.R,

Weidong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Weidong,

Does this test data based on read/ write full duples? If no, could you please help provide the maximum bandwidth of read/ write 8M.Mini PCIe at the same time?

BR, thanks.

Miles Lee

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can you clarify the data. Was the Endpoint the master and the RC the slave?

Did you do have any data with other side being the master?

Assuming the End Point is the master for this data, is there a reason the EP can accept data so much faster then the RC?