- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Observing half clock when accessing Quad SPI and Octal SPI memories in DDR mode

Hello,

We are using iMX8QXP MEK based custom board with Yocto L5.4.24-2.1.0. In our project, we are connecting multiple memories(like Octal SPI flash, Quad SPI flash, Octal SPI RAM) on the FlexSPI interface.

Our aim is to access these memories at the maximum possible speed. During read-write testing, we noticed that in SDR mode we are able to read-write memories at the clock frequency which we have set in the device tree file(spi-max-frequency property) but in DDR mode the frequency is halved.

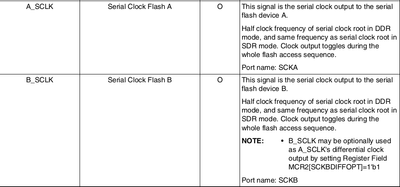

In the reference manual, we have seen the table 18.4 below which clearly states that the clock will be halved in DDR mode.

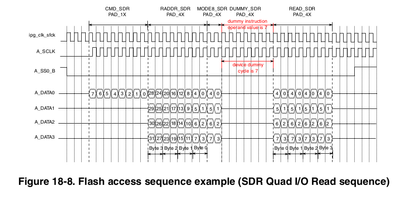

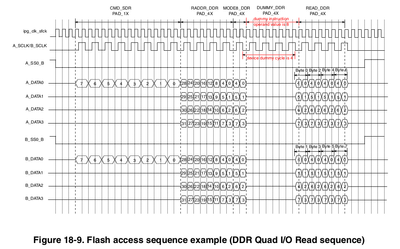

Also, the waveforms in the reference manual show half clock in DDR operations

From all these data from the reference manual, we understand that when we access memories in SDR mode the clock remains the same, but when we access memories in DDR mode the clock will get halved.

If the clock reduces by half during DDR, the actual data rate remains the same as during SDR and our actual goal of achieving the maximum data rate is not fulfilled.

1. Is this behavior correct?

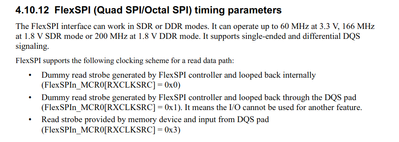

In the IMX8QXPAEC document, we have read the following under FlexSPI timing parameters.

2. Does this mean that we can access memories in DDR mode with the same frequency as SDR mode by changing MCR0[RXCLKSRC] register bits?

3. If yes, is there any document/procedure for that?

Thank you

Priyank

Hi priyank_bhatt

I think you are right, frequency can be changed using MCR0[RXCLKSRC] register

as described in Table 99-101 FlexSPI timings with FlexSPIn_MCR0

i.MX 8QuadXPlus and 8DualXPlus Automotive and Infotainment Applications Processors

Best regards

igor

He @igorpadykov

Thanks for the quick reply. I am a bit confused about that MCRO[RXCLKSRC].

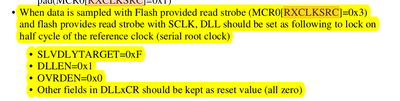

Because when I tried to change RXCLKSRC to 0x3 in flexSPI driver I observed kernel panic. Then after looking into the reference manual I found this statement

Thah is why I am asking if there is any document or procedure which I can follow to achieve proper clock?

Thank you.

Priyank

Hi Priyank

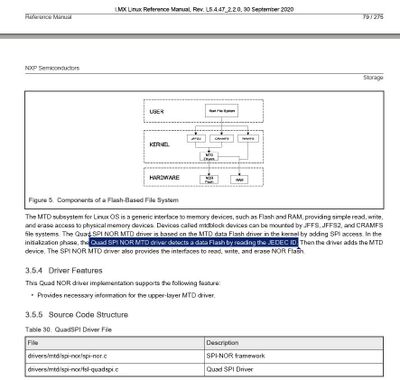

I am afraid you can not manually change frequency, as for example in

case for spi-nor usage, it is selected automatically by spi-nor driver

reading memory capabilities as described in JESD216 SFDP specification

Best regards

igor

Hi @igorpadykov

As per the reference manual

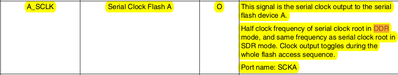

We are observing that in SDR mode we are getting the same clock frequency as serial clock and half clock frequency in DDR mode.

Is this the expected behavior?

Thank you.

Priyank

>Is this the expected behavior?

probably linux driver selects mode which is supported by that particular

spi-nor, one can try to debug fspi driver using AN 12631

Normal and Secure Debug for i.MX8/8X Family of Applications Processors

Best regards

igor

Hello,

I think there is some misunderstanding. I will again ask my query

As per reference manual IMX8DQXPRM Rev. E Table 18-4, it is mentioned that half clock frequency in DDR mode and the same frequency as the serial clock in SDR mode. We are also observing the same behavior.

Is this the expected behavior?

Thank you

Priyank

Hello

> it is mentioned that half clock frequency in DDR mode and the same frequency as the serial clock in SDR mode.

sorry this is not true, actually it describes:

Half clock frequency of serial clock root in DDR

mode, and same frequency as serial clock root in

SDR mode.

Serial clock root is not clock which you are observing.

>Is this the expected behavior?

in theory it should work as described in Reference Manual.

In real life it depends on many factors: used driver, operating system and attached devices.

In particular Reference Manual describes it :

Best regards

igor

Hi @igorpadykov

Thank you for your reply.

With the driver(spi_nor.c), operating system(Yocto L5.4.24-2.1.0) and Octal flash, Octal RAM, Octal MCP devices we observed that the frequency in DDR mode is getting halved compared to SDR mode frequency as mentioned in the reference manual.

Are there any changes we can do to get the same clock frequency in SDR and DDR mode?

Thank you.

had you verified with qspi datasheet, that its declared ddr mode frequency is more high

than observed ?

Best regards

igor

Hi @igorpadykov

The maximum supported clock frequency is 200MHz. Our main aim is to access memories with the same clock which we set in dts node.

But when we set max-spi-frequency as 200MHz in dts node and operate with DDR mode we only observe 100MHz on QSPI0A_SCLK pin.

Regards

Priyank

Hi Priyank

"set max-spi-frequency as 200MHz in dts" does not guarantee that part will operate at 200MHz.

Operating frequency is selected by reading qspi-nor capability as described in Linux Manual

so spi-nor.c driver reads Serial Flash Discoverable Parameters (SFDP) and sets operating frequency

according to data obtained from qspi-nor:

http://www.macronix.com/Lists/ApplicationNote/Attachments/1870/AN114v1-SFDP%20Introduction.pdf

Best regards

igor