- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: No data is received on I2C4_SCL and I2C4_SDA lines on iMx7DSABRESD board

No data is received on I2C4_SCL and I2C4_SDA lines on iMx7DSABRESD board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am working on iMx7DSABRESD board. I am configuring I2C4 device exposed as J20 connector (also named MFI). The pad settings that I have done are:

#define I2C4_CLK_ROOT 0x3038AF00

#define I2C4_CLK_ROOT_VALUE 0x11000001

#define IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_SYNC 0x30330210

#define IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_BCLK 0x30330214

#define IOMUXC_SW_PAD_CTL_PAD_SAI1_RX_SYNC 0x30330480

#define IOMUXC_SW_PAD_CTL_PAD_SAI1_RX_BCLK 0x30330484

#define IOMUXC_I2C4_SCL_SELECT_INPUT 0x303305EC

#define IOMUXC_I2C4_SDA_SELECT_INPUT 0x303305F0

/* Steps for the configuration

1. Write I2C4_CLK_ROOT_VALUE in I2C4_CLK_ROOT to enable the clock.

2. Select daisy chain values from the IOMUXC_I2C4_SCL_SELECT_INPUT and IOMUXC_I2C4_SDA_SELECT_INPUT registers by writing 0x03 to both.

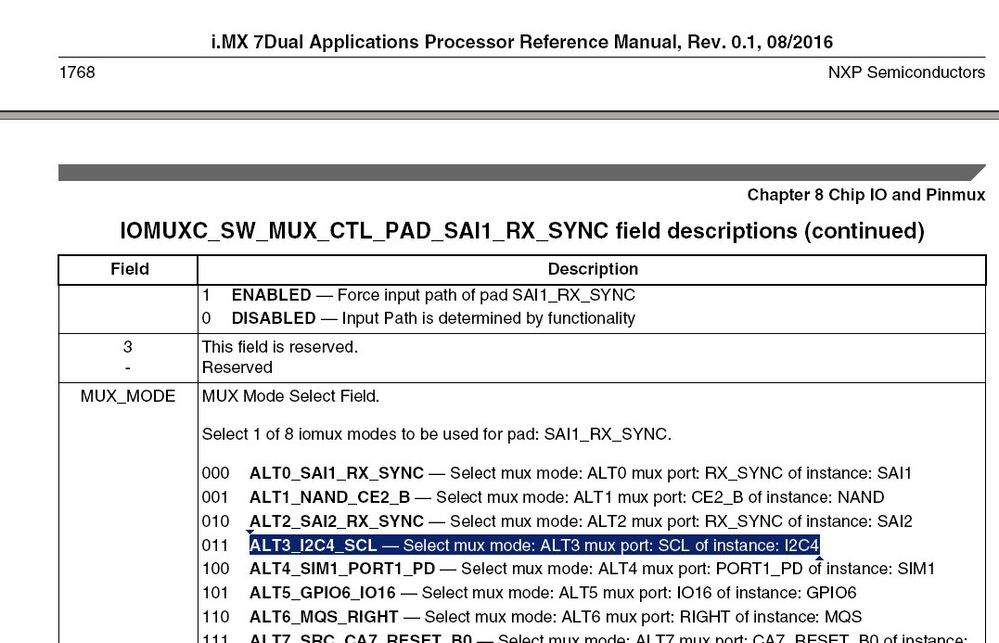

3. Write 0x03 to both IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_SYNC and IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_BCLK to ensure that I2C4 is selected.

4. Write 0x7F to both IOMUXC_SW_PAD_CTL_PAD_SAI1_RX_SYNC and IOMUXC_SW_PAD_CTL_PAD_SAI1_RX_BCLK to ensure the pad settings.

*/The problem is I get nothing except start and stop signals on the SCL and SDA lines. I don't get even these start and stop signals when I use any other pad except SAI1 registers.

I've also configured SAI1_RX_SYNC and SAI1_RX_BCLK as GPIO and toggled them and they are working perfectly.

The driver I am using for this device is working perfectly fine when I enable the I2C device of I2C3 module (exposed as J33 connector).

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amna

regarding IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_SYNC, seems for selecting

I2C4, ALT3 should be set (0x..13)

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amna

regarding IOMUXC_SW_MUX_CTL_PAD_SAI1_RX_SYNC, seems for selecting

I2C4, ALT3 should be set (0x..13)

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you. It solved my problem, but I still don't understand what enabling 'Force input path of pad SAI1_RX_SYNC' has to do with I2C4?