- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Masking MIPI CSI MASK1 register & MIPI CSI CRC Calculation

Masking MIPI CSI MASK1 register & MIPI CSI CRC Calculation

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Masking MIPI CSI MASK1 register & MIPI CSI CRC Calculation

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am working on a custom platform which is based on i.MX6Q + Xilinx Artix7. I'm using android Kitkat KK4.4.3 from Freescale. In the custom platform the Artix-7 FPGA acts as a MIPI CSI Transmitter, which keeps sending color bar data(YUV422) @720p 30fps, 200MHz (Discontinuous) to i.MX6Q. we tried to capture frame, but we noticed the MIPI_CSI_ERR1 register being set to 0x01001000. Based on the register description it is known that the CRC error is detected.

I have a couple of questions regarding Masking MIPI_CSI_MASK1 register and CRC Calculation

1) I tried masking those two error bits in MIPI_CSI_MASK1 register as shown below. However, I could see the MIPI_CSI_ERR1 bits are set to 0x01001000. On reboot also we are noticing the err bits are set.

How could i mask those error bits ? Is that anything i'm missing in my code ?

diff --git a/drivers/mxc/mipi/mxc_mipi_csi2.c b/drivers/mxc/mipi/mxc_mipi_csi2.c

index df45c36..de7dffc 100644

--- a/drivers/mxc/mipi/mxc_mipi_csi2.c

+++ b/drivers/mxc/mipi/mxc_mipi_csi2.c

@@ -291,8 +292,10 @@ int mipi_csi2_reset(struct mipi_csi2_info *info)

mipi_csi2_write(info, 0x00010044, MIPI_CSI2_PHY_TST_CTRL1);

mipi_csi2_write(info, 0x00000000, MIPI_CSI2_PHY_TST_CTRL0);

mipi_csi2_write(info, 0x00000014, MIPI_CSI2_PHY_TST_CTRL1);

mipi_csi2_write(info, 0x00000002, MIPI_CSI2_PHY_TST_CTRL0);

mipi_csi2_write(info, 0x00000000, MIPI_CSI2_PHY_TST_CTRL0);

+ mipi_csi2_write(info, 0x01001000, MIPI_CSI2_MASK1);

mipi_csi2_write(info, 0xffffffff, MIPI_CSI2_PHY_SHUTDOWNZ);

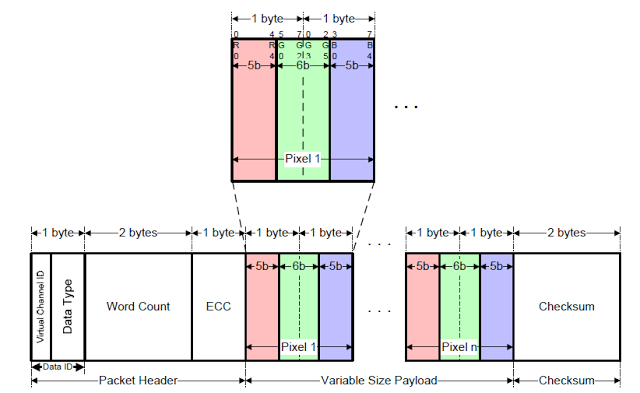

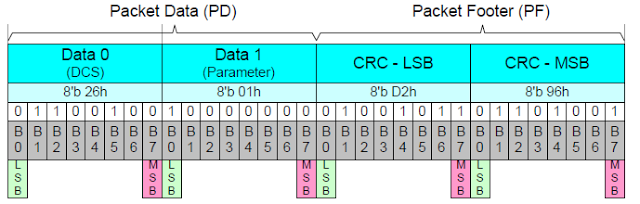

2) My MIPI CSI Knowledge is very minimum. Please correct me if i was wrong. Based on my understanding, Every MIPI Packet will have a 16bits CRC field at packet footer. As shown in the Figure 2, Some MIPI CSI Transceiver wll process the first CRC byte as LSB and then the MSB. Does i.MX6 MIPI CSI will also expects the same format or the reverse ?

FIg 1 : MIPI CSI Packet structure

FIg 2 : Packet Data and Packet Footer

3) As a question of curiosity, How CRC is calculated for MIPI CSI Packets ?

It would be helpful if you can share your thoughts for these questions. Thanks for your time.

Thanks

Shajin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shajin

1. MIPI_CSI_MASK1 register masks interrupts, it does not disable crc check

2. i.MX6 MIPI CSI uses this format, as defined in the MIPI CSI-2 Specification

3. MIPI CSI-2 Specification describes crc calculations, the generator polynomial is x16+x12+x5+x0

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

Thank you very much for the your response.

I would like to understand, If CRC Fails for the incoming Payload data, Whether it will discard the payload or still is it possible to dump the data to Memory ?

If it is possible to dump the data, please provide some pointers for capturing the data.

Regards

Shajin