- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- MMPF0100 PMIC compatibility for iMX6Q with LPDDR2

MMPF0100 PMIC compatibility for iMX6Q with LPDDR2

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MMPF0100 PMIC compatibility for iMX6Q with LPDDR2

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Karthik,

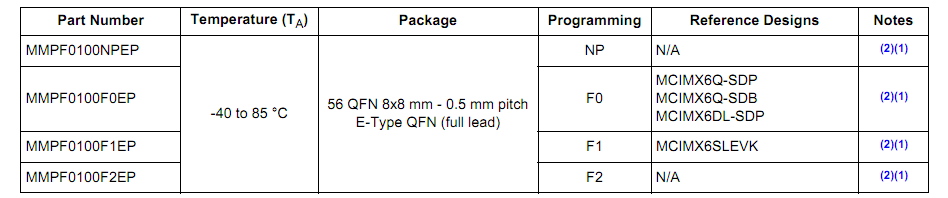

You can use F1 fuse option for your application with LPDDR2. and follow the reference design of MCIMX6SLEVK.

http://cache.freescale.com/files/product/hardware_tools/MCIMX6SLEVK.pdf

Depending on your application you may require LDO for other peripherals like LCD,which require 2.8V for IO supply.

If your project volume is low, you can go for customized OTP programming using KITPFPGMEVME.

Regards,

Rakhesh

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Karthik,

If none of the pre-programmed parts work for you, then you can order the PF-Programmer board and the socketed board and program parts for the voltages you require.

Here are the relevant links:

KITPF0100EPEVBE Product Summary Page

KITPF0100SKTEVBE Product Summary Page

The F2 sequence has SW3 output at 1.2V if that will work for you.

Regards,

Anand

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yongcai Huang,

Thanks for your reply. As you said, I hope 1.5 to 1.2 V LDO might be an appealing solution.

But Freescale should deliver PMIC customized for LPDDR2 as well in future.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Karthik

Please ask FAEs/PMIC experts first, maybe there is already solution of customized PMIC OCOTP. The additional LDO is only a back up plan, as it will bring power/cost penalty.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Karthik

From the fuse description of MMPF0100, the F1 and F0's differences are not just the DDR power rails' voltage difference, it also has many other differences. So, I think programming the OTP of PMIC to F1 is not proper, one solution came to my mind is, maybe you can contact PMIC's expert to see whether there is any way to just change the DDR power rails' voltage based on the F0's OCOTP setting. If not, then maybe you can consider adding hardware circuit to scale the DDR voltage from 1.5V to 1.2V based on F0's OCOTP setting, but it will bring in some power waste. So, I think you should contact the FAEs/PMIC's expert about the possibility of customizing OCOTP setting.