- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- MIPI DSI to Parallel chip bringup in iMX7d

MIPI DSI to Parallel chip bringup in iMX7d

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MIPI DSI to Parallel chip bringup in iMX7d

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using MIPI DSI to Parallel converter chip(TC358762) with iMX7d and we are experiencing problems reading registers from the the chip using the "mipi_dsi_pkt_read" function.

The error message is,

[ 3.655822] mxsfb 30730000.lcdif: registered mxc display driver mipi_dsi_samsung

[ 4.469595] mxc_mipi_dsi_samsung 30760000.mipi-dsi: wait rx done timeout!

[ 4.475087] mipid_tc358762_lcd_setup: MIPI DSI: mipi_dsi_pkt_read failed error = -110

However writing DSI regiters doesn't throw any error. But I want to read back the register values in TC358762 chip to ensure configurations written correctly. Because the chip is not responding to any register write.

My device tree entry for mipi_dsi is as follows,

&lcdif {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_lcdif>;

pinctrl-1 = <&pinctrl_lcdif>;

enable-gpio = <&gpio3 1 GPIO_ACTIVE_LOW>;

display = <&display0>;

disp-dev = "mipi_dsi_samsung";

status = "okay";

display0: display@0 {

bits-per-pixel = <24>;

bus-width = <24>;

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <27168240>;

hactive = <800>;

vactive = <480>;

hfront-porch = <50>;

hback-porch = <50>;

hsync-len = <2>; /*2*/

vback-porch = <10>;

vfront-porch = <10>;

vsync-len = <2>; /*2*/

hsync-active = <0>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <0>;

};

};

};

};

&mipi_dsi {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_mipi_dsi_reset>;

pinctrl-1 = <&pinctrl_mipi_dsi_reset>;

lcd_panel = "TRULY-WVGA-TC358762";

disp-power-on-supply = <®_mipi_dsi_pwr_on>;

resets = <&mipi_dsi_reset>;

status = "okay"; /* User will change the status from U-Boot */

};

mipi_dsi_reset: mipi-dsi-reset {

compatible = "gpio-reset";

reset-gpios = <&gpio1 2 GPIO_ACTIVE_LOW>;

reset-delay-us = <50>;

#reset-cells = <0>;

};

We have referred imx7d-sdb-mipi-dsi.dts and mxcfb_hx8363_wvga.c from linux-imx kernel for our driver development.

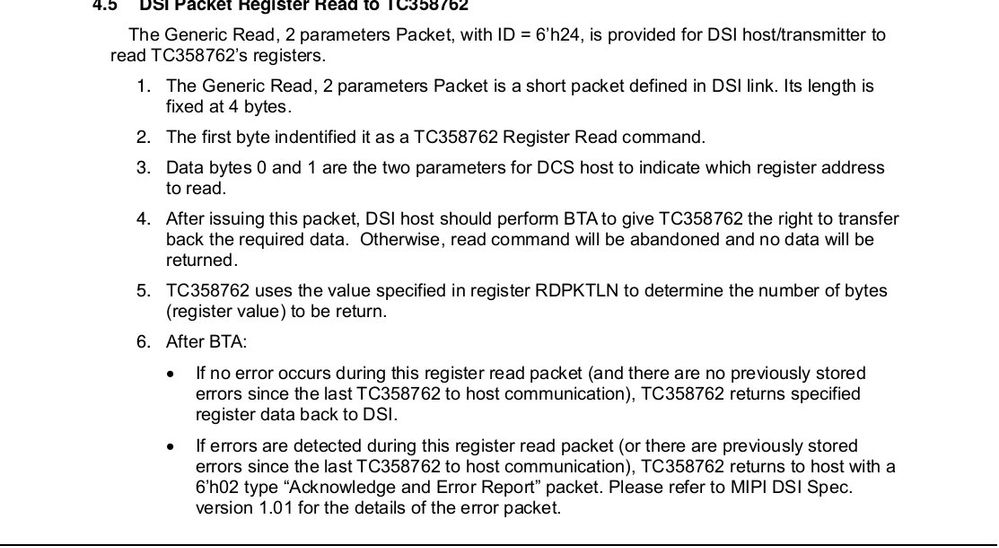

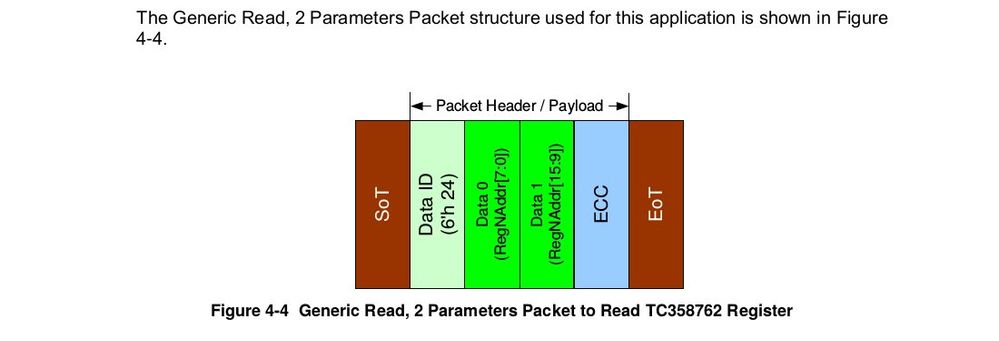

I hereby attached the DSI register read procedure from tc358762 data sheet.

We think that the DSI host not performing BTA (Bus Turn Around) properly to give TC358762 the right to transfer back the required data as mentioned in the datasheet? What do you think? Is there any other reason for this failure?

The sample read try of chip id from our driver

readdata[0] = 0xa0; //0xa0;

readdata[1] = 0x04; //0x04; (0x4a0 is the chip ID register)

readdata[2] = 0x00; //0x00;

readdata[3] = 0x00; //0x00;

readdata[4] = 0x00; //0x00;

readdata[5] = 0x00; //0x00;

err = mipi_dsi->mipi_dsi_pkt_read (mipi_dsi, MIPI_DSI_GENERIC_READ_REQUEST_2_PARAM, (u32 *)readdata, 4);

if (err < 0) {

printk ("%s: MIPI DSI: mipi_dsi_pkt_read failed error = %d\n",__func__, err);

return err;

}

Kindly help me to resolve this dsi read error.

Thanks,

Koil Arul Raj.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We proceed with i2c interface configuration of the chip registers, since the DSI interface register configuration not shown any progress.

Now we want to configure the iMX7 DSI clock as 360Mhz to generate 800x480 60Hz parallel RGB888 output from our DSI to parallel chip. As per TRM , the following formula is given to configure PLL output Frequncy(MIPI_DSI_PLLCTRL)

Fout = Fin x (M/ P x 2^S).

I am using following values, Fin = 24Mhz, M = 120, P=1, S= 3, It gives me, Fout = 360Mhz.

Is this correct? How to validate that PLL out frequency is configured correctly? Since MIPI Clock lines are differential lines (DSCP and DSCM), using DSO we get around 100Khz in each line. Is my calculations are correct in configuring DSI clock.

Based on our chip datasheet calculation, we are getting, the parallel output clock around 33MHz. But we are using following timing values with clock frequency of 27168240 for our output. Is this ok? Do you have any standard display timing parameters for 800x480 60Hz bpp=24 configuration?

&lcdif {

pinctrl-names = "default", "sleep";

pinctrl-0 = <&pinctrl_lcdif>;

pinctrl-1 = <&pinctrl_lcdif>;

enable-gpio = <&gpio3 1 GPIO_ACTIVE_LOW>;

display = <&display0>;

disp-dev = "mipi_dsi_samsung";

status = "okay";

display0: display@0 {

bits-per-pixel = <24>;

bus-width = <24>;

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <27168240>;

hactive = <800>;

vactive = <480>;

hfront-porch = <50>;

hback-porch = <50>;

hsync-len = <2>;

vback-porch = <10>;

vfront-porch = <10>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <0>;

};

};

};

};

Thanks,

Koil Arul Raj.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koil Arul Raj,

1. As per MIPI_DSI_PLLCTRL, if you use Fin = 24Mhz, M = 120, P=1, S= 3 and formula Fout = Fin x (M/ P x 2^S),

then it will be Fout as 11.25.

PMS_S (Specifies the PLL PMS value for the S divider) = 3 , means it will divide by 8. So the above formula will give 11.25.

2. For the resolution you are trying to configure, you can check out the device tree for i.MX7D to get the default configuration parameter. For example, this snippet is from imx7d-nitrogen7.dts

&lcdif {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lcdif_dat

&pinctrl_lcdif_ctrl>;

lcd-supply = <®_vref_3v3>;

display = <&display0>;

status = "okay";

display0: lcd-display {

bits-per-pixel = <16>;

bus-width = <18>;

display-timings {

native-mode = <&t_lcd>;

t_lcd: t_lcd_default {

/* default to Okaya display */

clock-frequency = <30000000>;

hactive = <800>;

vactive = <480>;

hfront-porch = <40>;

hback-porch = <40>;

hsync-len = <48>;

vback-porch = <29>;

vfront-porch = <13>;

vsync-len = <3>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <0>;

};

};

};

};Regards,

Ankit Patel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Koil

such errors may be caused by incorrect lcd power up sequence

and driver initialization, so one can check thoroughly if it's in accordance

with the lcd manual.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ankit/Igor,

Thanks for your reply.

We are still debugging the DSI read failure issue.

1. The error code -110 means ETIMEDOUT. The dsi read operation timedout when sending register read request using dsi link.

2. The source code versions,

Kernel - 4.9.11

Yocto - poky-morty V2.2

3. We checked that, the power up sequences are happening correctly. Also we could see activity in MIPI Data and clock lines in the input side of TC358762 chip. But there is no activity at output side clock (DCLK) and parallel data lines of the chip.

4. We use the following LCD config,

static struct mipi_lcd_config lcd_config = {

.virtual_ch = 0x0,

.data_lane_num = TC358762_TWO_DATA_LANE, // 2 data lanes

.max_phy_clk = TC358762_MAX_DPHY_CLK, // 800 MHz

.dpi_fmt = MIPI_RGB888,

};

Is there any basic DSI and clock related configuration we need to look after?

4. As per TC358762 data sheet, the Packet structure to Read TC358762 Register should be as follows,

But dsi_pkt_read function in mipi_dsi_samsung.c doesn't seems to write the complete packet. The code from the kernel driver writes only the packet id and MSB of register address as follows.

static void mipi_dsi_rd_tx_header(struct mipi_dsi_info *mipi_dsi,

u8 data_type, u8 data0)

{

unsigned int reg = (data_type << 0) | (data0 << 8);

writel(reg, mipi_dsi->mmio_base + MIPI_DSI_PKTHDR);

}

I tried modifying the code to write complete register address as below, but still the read fails.

static void mipi_dsi_rd_tx_header(struct mipi_dsi_info *mipi_dsi,

u8 data_type, u8 data0, u8 data1)

{

unsigned int reg = (data_type << 0) | (data1 << 8) | (data0 << 16);

writel(reg, mipi_dsi->mmio_base + MIPI_DSI_PKTHDR);

}

Does the mipi_dsi (mipi_dsi_samsung.c) interface support two byte register address read?

Thanks,

Koil Arul Raj.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koil Arul Raj,

Can you let us know what does the -110 error code indicates? This seems to be MIPI specific so you might get that from MIPI specification.

Can you let us know which kernel & yocto version are you using?

Have you gone through the iMX 7d reference manual topic 13.4.3.10.2 Programming model ? Checkout the command mode in BTA case in the given table. Also, please check the ESCPRESCALER field in MIPI_DSI_CLKCTRL register which has a NOTE for BTA.

Regards,

Ankit Patel