- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: MIMXRT685S-AUD_EVK Wire ACK Fault in DAP access

MIMXRT685S-AUD_EVK Wire ACK Fault in DAP access

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have been unsuccessful in actually running any of the demo projects for the 685S audio EVK. Each time I attempt time, I try to select debug using the LinkServer Probes and I get the following output connected to J5 with SW5 set to 010:

Probe Firmware: LPC-LINK2 CMSIS-DAP V5.361 (NXP Semiconductors)

Serial Number: FTA2BQIR

VID:PID: 1FC9:0090

USB Path: /dev/hidraw4

Using memory from core 0 after searching for a good core

processor is in secure mode

warning - watchpoint hit but none found set

debug interface type = CoreSight DP (DAP DP ID 6BA02477) over SWD TAP 0

processor type = Cortex-M33 (CPU ID 00000D21) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 6BA02477. CpuID: 00000D21. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FE000: CID B105100D PID 0000095000 ROM (type 0x1)

ROM 1 E00FF000: CID B105100D PID 04000BB4C9 ROM (type 0x1)

ROM 2 E000E000: CID B105900D PID 04000BBD21 CSt ARM ARMv8-M type 0x0 Misc - Undefined

ROM 2 E0001000: CID B105900D PID 04000BBD21 CSt ARM DWTv2 type 0x0 Misc - Undefined

ROM 2 E0002000: CID B105900D PID 04000BBD21 CSt ARM FPBv2 type 0x0 Misc - Undefined

ROM 2 E0000000: CID B105900D PID 04000BBD21 CSt ARM ITMv2 type 0x43 Trace Source - Bus

ROM 2 E0041000: CID B105900D PID 04002BBD21 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04000BBD21 CSt ARM CTIv2 type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BBD21 CSt type 0x11 Trace Sink - TPIU

NXP: MIMXRT685S

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT600_FlexSPI_B_MXIC_OPI.cfx

Image 'MIMXRT600_FlexSPI_B_MXIC_OPI Jul 25 2023 09:13:28'

Opening flash driver MIMXRT600_FlexSPI_B_MXIC_OPI.cfx

VECTRESET requested, but not supported on ARMv8-M CPUs. Using SOFTRESET instead.

Using SOFT reset to run the flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (64MB = 1024*64K at 0x8000000)

Closing flash driver MIMXRT600_FlexSPI_B_MXIC_OPI.cfx

Connected: was_reset=true. was_stopped=true

Awaiting telnet connection to port 3330 ...

GDB nonstop mode enabled

Opening flash driver MIMXRT600_FlexSPI_B_MXIC_OPI.cfx (already resident)

VECTRESET requested, but not supported on ARMv8-M CPUs. Using SOFTRESET instead.

Using SOFT reset to run the flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (64MB = 1024*64K at 0x8000000)

Writing 28172 bytes to address 0x08000000 in Flash

Sectors written: 0, unchanged: 1, total: 1

Erased/Wrote sector 0-0 with 28172 bytes in 25msec

Closing flash driver MIMXRT600_FlexSPI_B_MXIC_OPI.cfx

Flash Write Done

Flash Program Summary: 28172 bytes in 0.03 seconds (1100.47 KB/sec)

Starting execution using system reset and halt target with a stall address

Retask read watchpoint 1 at 0x50002034 to use for boot ROM stall

processor is in non-secure mode

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

Warning - processor did not halt - gave up waiting

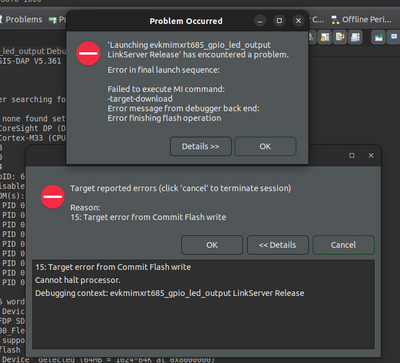

flash - system reset failed - Ep(04). Cannot halt processor.

Target error from Commit Flash write: Ep(04). Cannot halt processor.

GDB stub (/usr/local/mcuxpressoide-11.8.0_1165/ide/plugins/com.nxp.mcuxpresso.tools.bin.linux_11.8.0.202307121428/binaries//crt_emu_cm_redlink) terminating - GDB protocol problem: Pipe has been closed by GDB.

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

I have tried using the SPT to do a mass erase by first setting SW5 to 110 and then connecting to J7. The EVK is found and it appears that an erase is successful, but when I return everything to the original settings and plug back into J5, I continue to get these errors. What could I be missing? And it does seem that when I initially plugged this board in that the blinky LED example that was preloaded was not actually running (at least the user LED was not flashing).

Thanks, Matt

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrichardson ,

I know why you can't work!

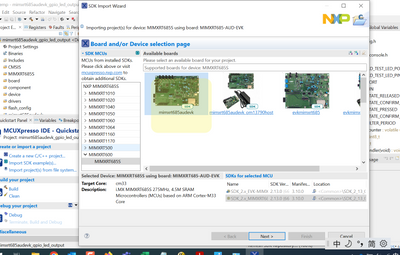

Not only the .cfx issues, you are totally using the wrong SDK.

You are using the MIMXRT685-EVK SDK, not the MIMXRT685-AUD-EVK.

Please download this SDK, drag it to the mcuxpresso, import it again:

https://mcuxpresso.nxp.com/en/builder?hw=MIMXRT685-AUD-EVK

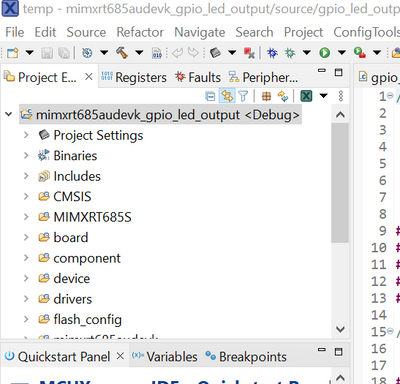

This project name should be like this:

Before you download this code, please do the mass erase at first.

As your downloaded code with the wrong FCB for the MIMXRT685-AUD-EVK, then core can't find the correct entry point, then it will meet your debug issues, you also can enter the ISP mode to download at first, the exit, switch to internal boot mode again to test it, then it will works.

Please try it, I can make sure you can make it work after you do the masserase and use the correct SDK project.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

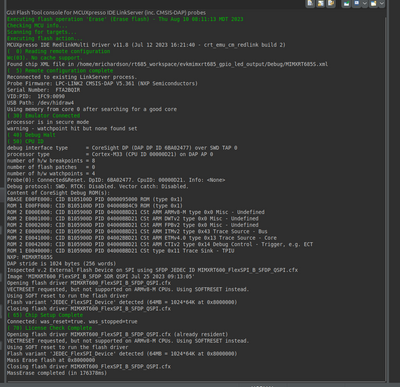

Doesn't look like it works:

MCUXpresso IDE RedlinkMulti Driver v11.8 (Jul 12 2023 16:21:40 - crt_emu_cm_redlink build 2)

Found chip XML file in /home/mrichardson/rt685_workspace/evkmimxrt685_gpio_led_output/Debug/MIMXRT685S.xml

Reconnected to existing LinkServer process.

Probe Firmware: LPC-LINK2 CMSIS-DAP V5.361 (NXP Semiconductors)

Serial Number: FTA2BQIR

VID:PID: 1FC9:0090

USB Path: /dev/hidraw4

Using memory from core 0 after searching for a good core

processor is in secure mode

debug interface type = CoreSight DP (DAP DP ID 6BA02477) over SWD TAP 0

processor type = Cortex-M33 (CPU ID 00000D21) on DAP AP 0

number of h/w breakpoints = 8

number of flash patches = 0

number of h/w watchpoints = 4

Probe(0): Connected&Reset. DpID: 6BA02477. CpuID: 00000D21. Info: <None>

Debug protocol: SWD. RTCK: Disabled. Vector catch: Disabled.

Content of CoreSight Debug ROM(s):

RBASE E00FE000: CID B105100D PID 0000095000 ROM (type 0x1)

ROM 1 E00FF000: CID B105100D PID 04000BB4C9 ROM (type 0x1)

ROM 2 E000E000: CID B105900D PID 04000BBD21 CSt ARM ARMv8-M type 0x0 Misc - Undefined

ROM 2 E0001000: CID B105900D PID 04000BBD21 CSt ARM DWTv2 type 0x0 Misc - Undefined

ROM 2 E0002000: CID B105900D PID 04000BBD21 CSt ARM FPBv2 type 0x0 Misc - Undefined

ROM 2 E0000000: CID B105900D PID 04000BBD21 CSt ARM ITMv2 type 0x43 Trace Source - Bus

ROM 2 E0041000: CID B105900D PID 04002BBD21 CSt ARM ETMv4.0 type 0x13 Trace Source - Core

ROM 2 E0042000: CID B105900D PID 04000BBD21 CSt ARM CTIv2 type 0x14 Debug Control - Trigger, e.g. ECT

ROM 1 E0040000: CID B105900D PID 04000BBD21 CSt type 0x11 Trace Sink - TPIU

NXP: MIMXRT685S

DAP stride is 1024 bytes (256 words)

Inspected v.2 External Flash Device on SPI using SFDP JEDEC ID MIMXRT600_FlexSPI_B_SFDP_QSPI.cfx

Image 'MIMXRT600_FlexSPI_B_SFDP SDR QSPI Jul 25 2023 09:13:05'

Opening flash driver MIMXRT600_FlexSPI_B_SFDP_QSPI.cfx

VECTRESET requested, but not supported on ARMv8-M CPUs. Using SOFTRESET instead.

Using SOFT reset to run the flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (64MB = 1024*64K at 0x8000000)

Closing flash driver MIMXRT600_FlexSPI_B_SFDP_QSPI.cfx

Connected: was_reset=true. was_stopped=false

Awaiting telnet connection to port 3330 ...

GDB nonstop mode enabled

Opening flash driver MIMXRT600_FlexSPI_B_SFDP_QSPI.cfx (already resident)

VECTRESET requested, but not supported on ARMv8-M CPUs. Using SOFTRESET instead.

Using SOFT reset to run the flash driver

Flash variant 'JEDEC_FlexSPI_Device' detected (64MB = 1024*64K at 0x8000000)

Writing 28172 bytes to address 0x08000000 in Flash

Sectors written: 0, unchanged: 1, total: 1

Erased/Wrote sector 0-0 with 28172 bytes in 19msec

Closing flash driver MIMXRT600_FlexSPI_B_SFDP_QSPI.cfx

Flash Write Done

Flash Program Summary: 28172 bytes in 0.02 seconds (1447.99 KB/sec)

Starting execution using system reset and halt target with a stall address

Retask read watchpoint 1 at 0x50002034 to use for boot ROM stall

processor is in non-secure mode

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

Warning - processor did not halt - gave up waiting

flash - system reset failed - Ep(04). Cannot halt processor.

Target error from Commit Flash write: Ep(04). Cannot halt processor.

GDB stub (/usr/local/mcuxpressoide-11.8.0_1165/ide/plugins/com.nxp.mcuxpresso.tools.bin.linux_11.8.0.202307121428/binaries//crt_emu_cm_redlink) terminating - GDB protocol problem: Pipe has been closed by GDB.

state - running or following reset request - re-read of state failed - rc Nn(05). Wire ACK Fault in DAP access

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrichardson ,

Your orignal log is the wrong .cfx, that is used for the EVK octal flash.

AUD-EVK is the QSPI flash.

To the secure, it is the none-secure mode, it is correct.

Now, you still have issues, please use the MCUbootUtility to the mass erase at first in the ISP mode, then back to the internal boot mode do the debug again.

Any issues, kindly let me know.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @kerryzhou. I did a complete erase using the secure provisioning tool and got the same result when trying to debug again.

Then did a mass erase via the IDE and got this output:

Tried flashing and debugging again with exact same results as before.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And it seems that I am able to flash a new build of the blinky led example that ships with the kit using the SPT (verified that once board is rebooted, the user LED blinks). But if I reset SW5 to 010 and return the USB to J5 and then try to flash and debug, I get the same response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrichardson ,

I know why you can't work!

Not only the .cfx issues, you are totally using the wrong SDK.

You are using the MIMXRT685-EVK SDK, not the MIMXRT685-AUD-EVK.

Please download this SDK, drag it to the mcuxpresso, import it again:

https://mcuxpresso.nxp.com/en/builder?hw=MIMXRT685-AUD-EVK

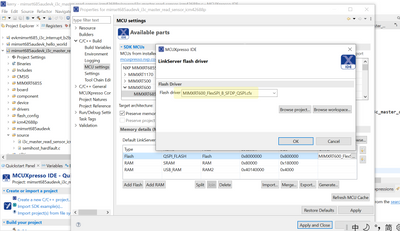

This project name should be like this:

Before you download this code, please do the mass erase at first.

As your downloaded code with the wrong FCB for the MIMXRT685-AUD-EVK, then core can't find the correct entry point, then it will meet your debug issues, you also can enter the ISP mode to download at first, the exit, switch to internal boot mode again to test it, then it will works.

Please try it, I can make sure you can make it work after you do the masserase and use the correct SDK project.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yay! That did it! And this is the reason the wrong cfx file came up. Thanks a bunch @kerryzhou!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are always welcome!

If you meet any issues in the future, welcome to create the new question post and let me know.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @mrichardson ,

You are using the wrong flashdriver.

The MIMXRT685-AUD-EVK is the QSPI flash, not the octal flash.

Please use this .cfx:

Then you will make it works.

Your select .cfx is the octal flash for the MIMXRT685-EVK, not the AUD-EVK.

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@kerryzhou What does it mean in the build messages that processor is in secure mode? Does this mean images have to be signed? I didn't explicitly set this up to be in a secure mode.