- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- MFGtools hangs on "Jumping to OS Image"

MFGtools hangs on "Jumping to OS Image"

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MFGtools hangs on "Jumping to OS Image"

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

According to the reference design of I.MX6 SabreSD board, we design our circuit boards. Recently, we have producted 400 boards, There were almost 70 abnormal boards. When we download software into boards by MFGtools, it hangs on "Jumping to OS Image", and there is nothing at UART port (debug port). The other 330 circuit boards are OK,

the software can be downloaded successfully, and also these boards can boot from eMMC successfully.

We don't use DDR3 MT41K128M16JT-125:K from MICRON, and we use SCN15H2G1 60AF-13K from UnilC. SCN15H2G1 60AF-13K and MT41K128M16JT-125:K are with the same parameters such as max clock frequency 800M (DDR3-1600), 2Gbit (128M x 16) and so on. We have done DDR calibration, DDR pressure Test, update file "flash_header.s", rebuild our firmware and MFGtool's firmware ( uboot and kernal), replace the files

For 70 abnormal boards,what we have done are as follows:

1) We measure all the voltages and power-on sequence of the board, they are OK;

2) We do DDR pressure Test, and they are OK;

What's the problem? Why some baords are OK,and others are not OK?

Attachments are Mfgtoos.log and DDR's datasheet.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pu

reason may be power board noise, as ddr test does not

sufficiently stress power subsystem of board. One can

check with oscilloscope ripples, ripple noise should be less

than 5% Vp-p of supply voltage average value.

Related power rails affected: all VDD_xxx_IN and VDD_xxx_CAP.

Please use guidelines of i.MX6 System Development User’s Guide

https://www.nxp.com/docs/en/user-guide/IMX6DQ6SDLHDG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, igor !

Thank you for your reply.

Here I have measured the power rails' ripple and noise as follows:

1) 1.5V for DDR, <40mV ripple and noise;

2) 1.35V for VDDARM_IN and VDDSOC, <30mV ripple and noise;

3) 3.3V for VDDHIGH_IN, eMMC and NVCC_xxx, <40mV ripple and noise;

4) 5V for USB,<70mV ripple and noise;

5) VDDARM_CAP, <20mV ripple and noise;

6) VDDSOC_CAP,<20mV ripple and noise;

7) VDDPU_CAP,<20mV ripple and noise;

8) VDDHIGH_CAP,<20mV ripple and noise;

All the power rails' ripple and noise is less than 3%.

What about other factors?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pu

you can also check clocks stability, for example change crystals

between boards.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

Firstly, I have exchanged the crystals 24MHz and 32.768KHz between good board and abnormal board, the problem was still not solved.

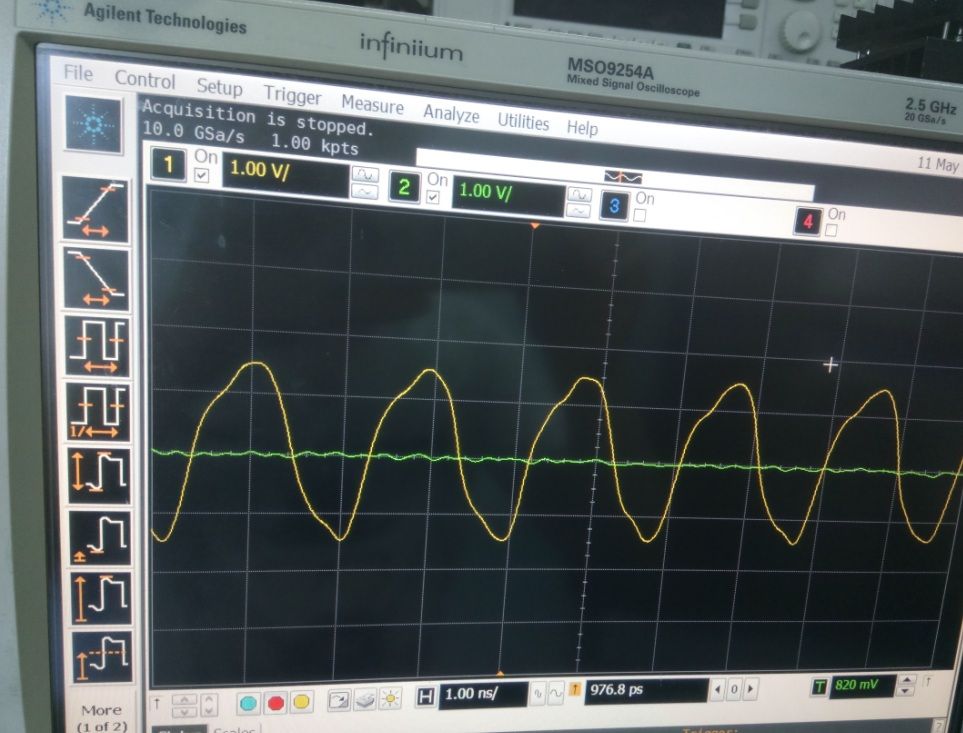

But I found an interesting phenomenon. When I tested signals DRAM_SDCLK1 or DRAM_SDCLK1_B between DDR and I.MX6D with oscilloscope, the software could be downloaded successfully.When software downloading, the probe of oscilloscope should be kept on the testpoint of DRAM_SDCLK1 or DRAM_SDCLK1_B, and should not be moved away. So what's the reason?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pu

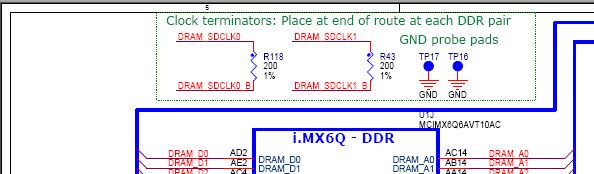

this may be caused by noise on SDCLK signals, on one can tweak termination resistors R118, R43

as depicted below from spf-27392 sabre sd schematic

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Igor.

I have exchanged resistors R118, R43 value from 200 to 130, 150, 220, and 270, the problem was still not solved. And when resistors R118, R43 value were 200, I have measured the signal SDCLK with oscilloscope, the signal was good.

So, what about other factors?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pu

also one can add small capacitors to decrease ringing.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, igor.

I finally found the reason.The amplitude of DRAM_SDCLK0 was about 1V smaller than the amplitude when the board was OK, because one DDR was not soldered well. After I heated the DDR, the amplitude of DRAM_SDCLK0 was OK.

I removed the R118 and R43, and replaced them with 2.7pF capacitors, the software could be downloaded successfully, and also these boards could boot from eMMC successfully.

So, I replace R118 and R43 200Ω with 2.7pF capacitors, the Vp-p amplitude of DRAM_SDCLK0 and DRAM_SDCLK1 is about 3.0V, Is there any risk?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pu

replacing R118 and R43 200Ω with 2.7pF capacitors seems as

good as @528Mhz it gives about 100Ohm as requires Hardware Guide for

differential lines impedances.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你好,我现在也遇到类似问题,之前还是好的板子烧录不成功了,一直在jump to os 界面,你这个问题后来是啥原因?如何对策了?另外我们还出现概率性系统第一次上电起不来问题!有啥建议?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你好,tommy。建议:1)对单板做DDR压力测试,多测试几次,看看是否有异常;2)针对概率性启动问题,检查一下上电时序,以及32.768KHz晶体是否焊接。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, igor.

Resistors R118, R43 value were 200 in abnormal board, one board sometimes was OK and sometimes was abnormal. When the board was abnormal, the amplitude of DRAM_SDCLK0 was about 1V smaller than the amplitude when the board was OK.