- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

MCIMX6G3CVM05AA reset circuit

Hello,

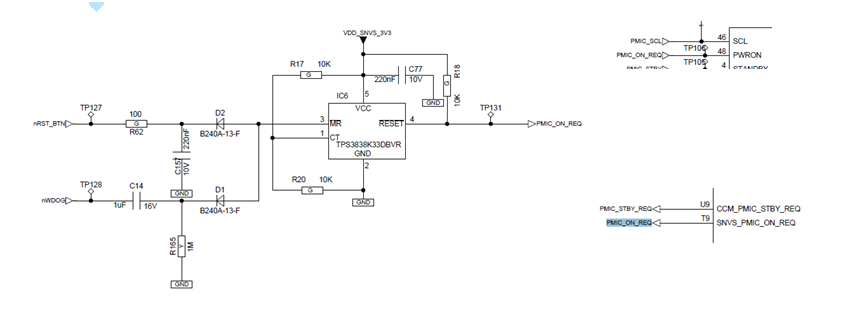

We are using POR (P8) signal to reset the CPU. Here the reset to this pin is done by ORing the following reset sources. 1.Reset using Power-On Reset chip

2.Reset using Watch dog timer chip

3.Reset using Undervoltage/Overvoltage monitor chip

4.Reset using PMIC reset out

The same is shown in the attached images.

Now please let me know if my reset startegy is correct or not. Do I need to take care of something else.

Regards

Dear Igor,

Thanks a lot for your reply.

I went through i.MX6UL EVK schematic SPF-28617, where I learned that supervisory reset chip U708 is used to drive Enable pin of main switcher. Enable is also controlled through MX6_POR_B(Tact switch) and nWDOG.

In my circuit I have used separate pin to reset eMMC. DDR3L is also having its own reset input driven through CPU.

eCSPI is also having a dedicated reset using GPIO pin of CPU.

Now my concern is with CPU that I want to reset the CPU in case of follwoing events.

1. External Watch dog timer timeout event

2.Undervoltage on any critical power(Which we are monitoring)

3.Reset event from PMIC (RESETBMCU)

As I shown in earlier image where I am ORing these above three inputs and in case of above condition is true, a RESET on POR of the CPU is generated.

Please once again let me knwo your inputs on this.

Regards,

Surendra

Hi Surendra

in attached image it is not shown that all power supplies of board are reset.

Please verify that this resets all board power supplies

Best regards

igor

Hello Igor,

Please find the attached image where it shows that PMIC_ON_REQ pin is generated by CPU on T9 pin. When this is generated either by CPU or Internal watchdog or external reset switch, PMIC chip PWRON pin is driven.

In this case PMIC chip may go in OFF state or sleep mode. This shall disable power of all the chips available on board such as eMMC, DDR3L and others.

In case of external watchdog miss event or undervoltage, POR_B is generated which shall drive POR pin of the CPU only and put the CPU to reset.

In other words external switch, Internal watchdog or CPU can drive PWRON of PMIC which shall power down for all the available chips on board.

In case when there is external watchdog miss event or undervoltage on power rail is detected only CPU is resetted using POR pin.

Regards,

Surendra

Hi Surendra

if PMIC chip PWRON pin is driven by reset then this is fine solution.

Best regards

igor

Hi Surendra

recommended to perform whole board reset as it is done in

i.MX6UL EVK schematic SPF-28617 using U708 (POR,WDOG) and

gating DCDC_3V3, as some components are not reset with POR only,

these include (but may not be limited to):

• eMMC memory card (if the hardware RST_B pin is not connected.

• SD Card/socket (if the reset pin is not used to remove power to the SD Card)

• QSPI

• LPDDR2/3 memory

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------