- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: LPDDR4 RPA configuration with custom iMX8M Plus Board

LPDDR4 RPA configuration with custom iMX8M Plus Board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

When trying to run the DDR training, the following error occurs, while using Mscale_ddr_tool _v3.20:

"PMU: Error: CA Training Failed.

PMU: ***** Assertion Error - terminating *****"

Find attached the MX8M_Plus_LPDDR4_RPA_v6 for my 4GB LPDDR4.

Further infos:

- Custom board using i.MX8M-Plus

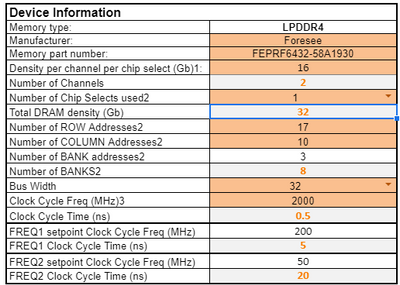

- LDDR4+eMMC: FORESEE_eMCP_FEPRF6432-58A1930 Twin die (please see datasheet attached p34)

Could you please check my RPA (xlsx) configuration attached?

The datasheet says "number of ROW adress R[16:0] but it seems invalid for the RPA files.

Thank you

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Maxime

from team:

-------------------------

I'm not very clear about customer's DDR configuration.

From the DDR device datasheet they used is a two die ddr, and one channel in one die, and 16Gb per die, and 16dq per die.

So, if customer want to config 32bit, they just need config two channels and one "chip select".

What does customer mean "use 2 chip select per channel". 8Gb per channel per chip select is not allowed in datasheet.

-------------------------

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Maxime,

I also had this issue before.

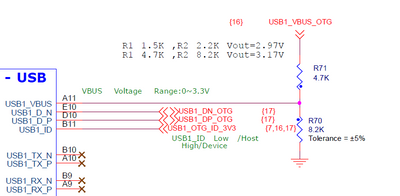

But I had change USB1_VBUS input.

R71 = 30K , R72 is DNP.

It can finish DDR calibration function.

Just share this information to you.

My DRAM is single die 16Gbit. , DRAM total size is 32Gbit.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

could you please provide part of schematic with ddr connections.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Maxime

from team:

-------------------------

I'm not very clear about customer's DDR configuration.

From the DDR device datasheet they used is a two die ddr, and one channel in one die, and 16Gb per die, and 16dq per die.

So, if customer want to config 32bit, they just need config two channels and one "chip select".

What does customer mean "use 2 chip select per channel". 8Gb per channel per chip select is not allowed in datasheet.

-------------------------

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

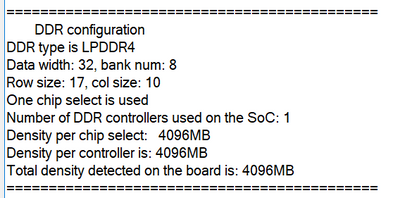

As I said, I use 4GB LPDDR4 with 1 CS per channel of 16Gb as shown in the RPA file attached. So for me it seems ok, I have 2 channels with 1 CS on each channel then 32Gb memory.

But when I start the DDR stress test, it shows that I have 1 CS with 32GB :

I would expect 2 CS with 4GB or 1CS with 2GB. The total is ok but I am having problem with the memory map in early Android boot with this config. Can you confirm my config is ok?

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告