- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- LPDDR Memory Testing Issue on Custom IMX93 Board

LPDDR Memory Testing Issue on Custom IMX93 Board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPDDR Memory Testing Issue on Custom IMX93 Board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Experts,

I'm working on a custom board based on the IMX93. While testing at the U-Boot level, we are using a 2GB LPDDR memory module.

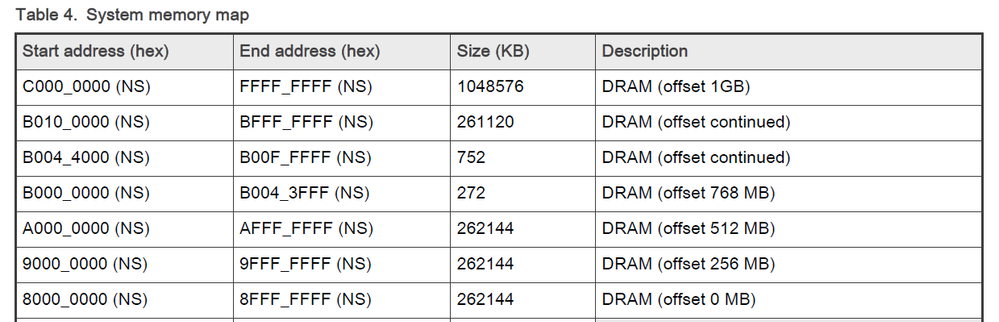

According to the IMX93 Reference Manual, we tested the system memory map using the mtest command from the start address 0x80000000 (NS) to the end address 0xBFFFFFFF (NS). This range is functioning correctly, with both read and write operations working as expected.

But, when performing mtest from 0xC0000000 to 0xFFFFFFFF, it fails, as shown in the diagram below.

i followed the mtest as per the : mtest

Could you please provide insights into why this issue occurs and possible solutions?

Thanks & Regards

Ravikumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JorgeCas

Yes, I've tested with DDR Data Rate with 1866 Mbps including/excluding multiple set point. so at this case all test are passing without any target board connection issues.

Thanks & Regards

Ravikumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You should take DDR tool stress test as final result since there are some RAM sections reserved for the system. Causing writing/reading errors, unexpected reset or system hang.

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I tested with the DDR Tool stress test, and it passed. After that, I ran the memory test (mtest) at the boot stage in the console.

Can you tell me which RAM sections are causing the read/write errors?

Thanks & Regards,

Ravikumar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please check it with bdinfo command:

u-boot=> bdinfo

boot_params = 0x0000000000000000

DRAM bank = 0x0000000000000000

-> start = 0x0000000080000000

-> size = 0x0000000016000000

DRAM bank = 0x0000000000000001

-> start = 0x0000000098000000

-> size = 0x0000000068000000

flashstart = 0x0000000000000000

flashsize = 0x0000000000000000

flashoffset = 0x0000000000000000

baudrate = 115200 bps

relocaddr = 0x00000000feeeb000

reloc off = 0x000000007eceb000

Build = 64-bit

current eth = ethernet@428a0000

eth1addr = 00:04:9f:08:78:d7

IP addr = <NULL>

fdt_blob = 0x00000000fcedd730

new_fdt = 0x00000000fcedd730

fdt_size = 0x000000000000d640

Video = lcd-controller@4ae30000 inactive

lmb_dump_all:

memory.cnt = 0x2 / max = 0x10

memory[0] [0x80000000-0x95ffffff], 0x16000000 bytes flags: 0

memory[1] [0x98000000-0xffffffff], 0x68000000 bytes flags: 0

reserved.cnt = 0x2 / max = 0x10

reserved[0] [0xfbed3000-0xffffffff], 0x0412d000 bytes flags: 0

reserved[1] [0xfced90b0-0xffffffff], 0x03126f50 bytes flags: 0

devicetree = separate

arch_number = 0x0000000000000000

TLB addr = 0x00000000fffe0000

irq_sp = 0x00000000fcedd720

sp start = 0x00000000fcedd720

Early malloc usage: 16e68 / 18000Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Did you test LPDDR memory with our stress DDR Tool?

Best regards.