- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

IMX6ULL with codec MAX98090

Hello all,

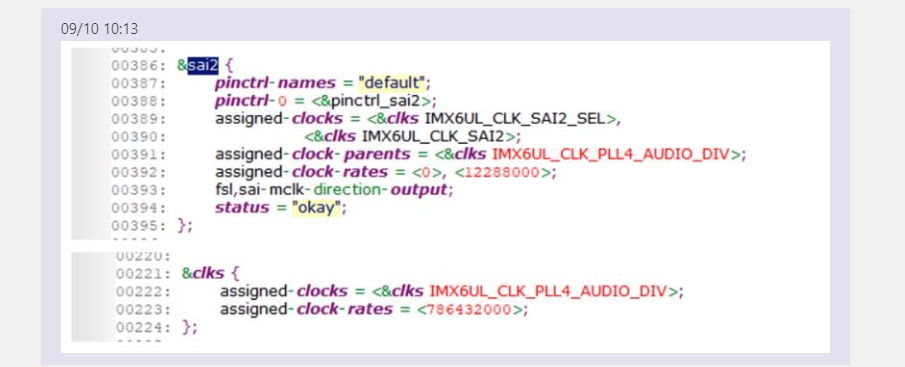

i need to configure the IMX pin that control the LRCLK pin of the MAX98090 as outpout beacuse i have problem with the clock signal levels. For the MCLK we have do that in this way:

how can i do the same for the LRCLK pin that is connected to the SAI_SYNC pin?

Thanks

Hi Daniele

one can look at i.MX6ULL EVK wm8960 example :

imx6ull-14x14-evk.dts\dts\boot\arm\arch - linux-imx - i.MX Linux kernel

i.MX6ULL EVK schematic

Design files, including hardware schematics, Gerbers, and OrCAD files

may be useful to check sai dts documentation:

fsl-sai.txt\sound\bindings\devicetree\Documentation - linux-imx - i.MX Linux kernel

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello,

thanks we are trying to understand if the configuration of the pins is correct for our MAX98090 that is different from the wm8960 . We have set the fsl,pins in this way:

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x170A1

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x170A1

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x110A0

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x110A0

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x170A1

>;

};

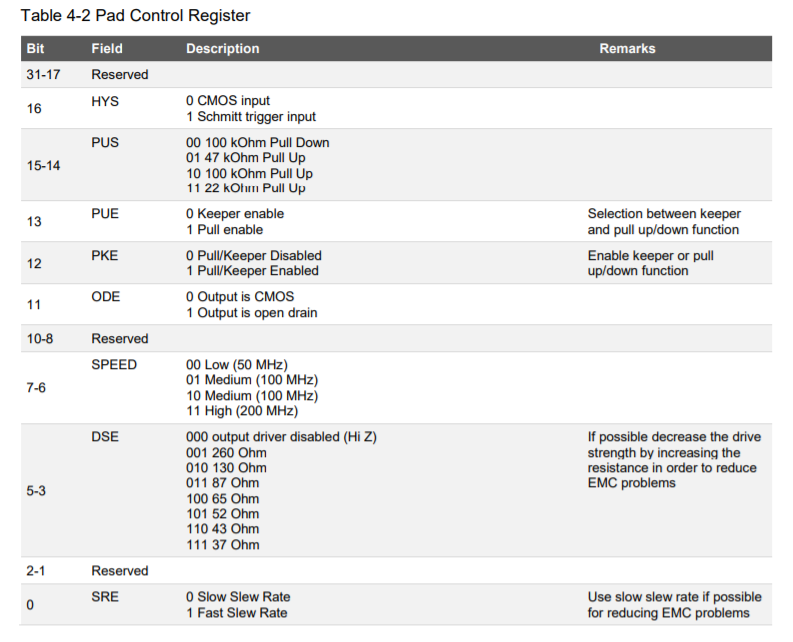

reducing the DSE resistence and enabling the fast slew rate

we have seen that the PAD define are:

* The pin function ID is a tuple of

* <mux_reg conf_reg input_reg mux_mode input_val>

*/

so had you checked signals with oscilloscope,

do they suit MAX98090 datasheet requirements ?

Best regards

igor

Hello,

we are trying to increase the clock signal quality changing the DSE configuration of the pins following the guide on pag 19 of this document https://docs.toradex.com/104446-colibri-arm-som-imx6ull-datasheet.pdf

Thanks