- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IMX6UL ethernet does work in u-boot but it doesn't with Kernel 3.14.38

IMX6UL ethernet does work in u-boot but it doesn't with Kernel 3.14.38

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everybody,

My partner Goiatz Leibar and me are facing this issue.

First of all, say we have a customized board with the IMX6UL processor. and with the kernel 3.14.38-6UL

The fact is that we got ethernet working in u-boot but not in kernel.

We use ENET1 and as we also use the GPIO1_IO06 and GPIO1_IO07 for other purposses, the MDIO and MDC are in "ENET2_RX_DATA0 and ENET2_RX_DATA1"

In U-BOOT (working fine)

This are the chages so ethernet works in u-boot.

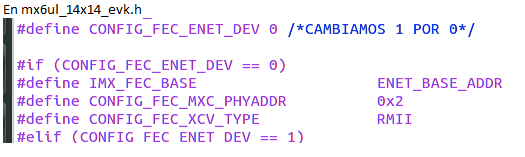

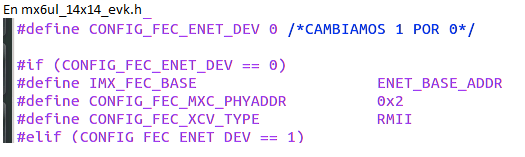

We select FEC 0, (mx6ul_14x14_evk.h)

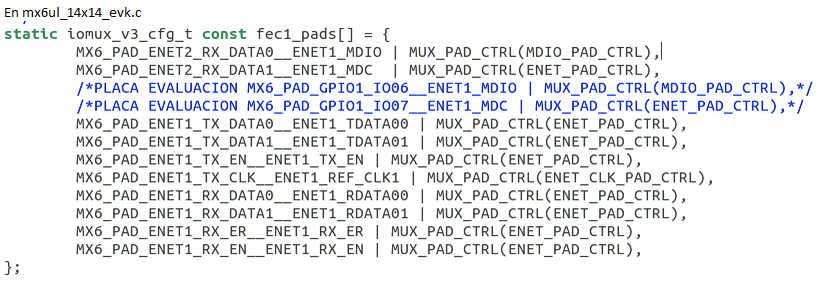

We change the MDIO and MDC pins (mx6ul_14x14_evk.c)

In Kernel

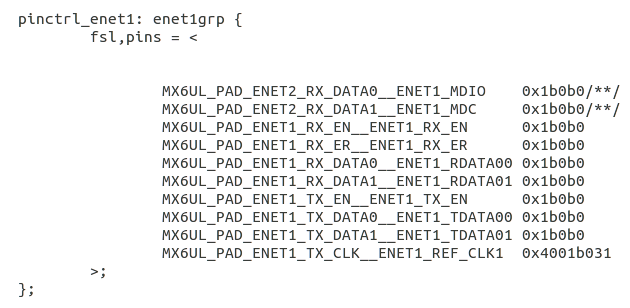

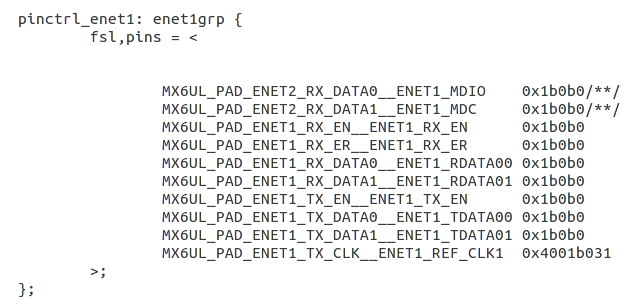

But when we try to make it works in kernel, we do the following with no succsses

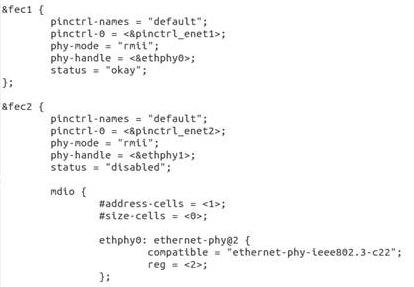

In kernel's device tree (imx6ul14x14-evk.dts):

We disable FEC2 and we also add our board pins

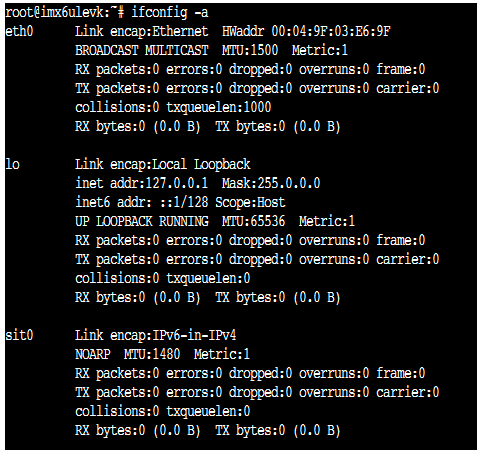

Once the system has booted, we make an "ifconfig -a" and here you can see how MAC address is the one we asigned before in u-boot.

Please find attached the .log file when the board boots

Original Attachment has been moved to: Custom_boot.txt.zip

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alberto Lubeiro ,

If you disable FEC2, you need to add mdio to FEC1, like this:

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <2>;

};

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

};

};

};

&fec2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet2>;

phy-mode = "rmii";

phy-handle = <ðphy1>;

status = "disabled";

};

And this change in the FEC1 pins:

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

MX6UL_PAD_GPIO1_IO06__ENET1_MDIO 0x1b0b0

MX6UL_PAD_GPIO1_IO07__ENET1_MDC 0x1b0b0

>;

};

These changes disable FEC2 in EVK and FEC1 works.

Luis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alberto Lubeiro ,

If you disable FEC2, you need to add mdio to FEC1, like this:

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <2>;

};

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

};

};

};

&fec2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet2>;

phy-mode = "rmii";

phy-handle = <ðphy1>;

status = "disabled";

};

And this change in the FEC1 pins:

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

MX6UL_PAD_GPIO1_IO06__ENET1_MDIO 0x1b0b0

MX6UL_PAD_GPIO1_IO07__ENET1_MDC 0x1b0b0

>;

};

These changes disable FEC2 in EVK and FEC1 works.

Luis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a similar board, but the hardware guys made two more changes:

- PHY address changed to 1

- ENET1_nRST (the phy reset line) moved to GPIO2 IO10

My device tree changes are shown below, but ethernet is still not working in linux. Ethernet works from u-boot after changing CONFIG_FEC_ENET_DEV to 0.

The ethernet link light goes out at roughly the same time the "configuring network interfaces" message appears on the console:

Configuring network interfaces... fec 20b4000.ethernet eth0: Freescale FEC PHY driver [Micrel KSZ8081 or KSZ8091] (mii_bus:phy_addr=20b4000.ethernet:01, irq=-1)

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

Any suggestions about how to fix this?

Here are the relevant parts of my device tree (added phy-reset-gpios, changed phy address to 1 and added MDC and MDIO to pinctrl_enet1):

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

phy-reset-gpios = <&gpio2 10 0>; /* GPIO2_10, pin B14 */

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

};

};

};

...

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET2_RX_EN__GPIO2_IO10 0x0b0b0 /* ENET1_nRST (phy reset) */

MX6UL_PAD_GPIO1_IO07__ENET1_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET1_MDIO 0x1b0b0

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

>;

};

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Harvey,

Correct me if I am wrong but isn't the reset line on the PHY active low? If so then use the following line to setup the reset:

phy-reset-gpios = <&gpio2 10 GPIO_ACTIVE_LOW>; /* GPIO2_10, pin B14 */

You had <&gpio2 10 0> which is active high. It is recommended to use the GPIO_ACTIVE_HIGH and GPIO_ACTIVE_LOW defines instead of 0 and 1 to avoid confusion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Matthew, thanks for the quick reply.

The phy reset is indeed active low. However, ethernet still doesn't work after making the change. I checked the RST pin with a scope and it's high, so the PHY is not being held in reset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look closely at your PHY chip and check the P/N. Even the minor change on third line means change in id. And there is a bug in imx6ul fix to support this phy driver. In file arch/arm/mach-imx/mach-imx6ul.c in function __init imx6ul_enet_phy_init(void) bad mask is used in PHY id check phy_register_fixup_for_uid(PHY_ID_KSZ8081, 0xffffffff, ksz8081_phy_fixup); . You can try to fix it by chaging the mask to 0xffffff00 or include linux/micrel_phy.h and use MICREL_PHY_ID_MASK to fix it correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Jiri! That fixes my problem.

I included linux/micrel_phy.h and used MICREL_PHY_ID_MASK in arch/arm/mach-imx/mach-imx6ul.c and ethernet now comes up in linux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Luis,

Thanks! we have just added it and it works!

Thanks again and best regards.