- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- IMX6UL USB host problem

IMX6UL USB host problem

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

IMX6UL USB host problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi,

I am use platform is imx6ul, linux kernel 3.14.38 . I am use the imx6ul as the usb host device , when the usb in communication , I am pull out the usb port, the device prompt the error :

usb 1-1.2: device no response, device descriptor read/64, error -11 . How can I solve this problem ???

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

for dts options one can look in sect.41.2.6 Changing the Controller Operation Mode

attached Linux Manual. Also one can test with Demo Images

Latest L4.9.11 release :

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Which USB Device are you trying to connect to the processor ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I use imx6ul as usb device and other one imx6ul device as host . Devices use kernel code , it is printer driver code ,modify PID and UID, it can communicate to each other. Non communication, usb host and usb device plugged normal. Communication , usb host and usb device plugged abnormal, and the usb host prompt the error : usb 1-1.2: device no response, device descriptor read/64, error -11

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can you send me the DTS file where you changed the USB configuration to HOST ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

/*

* Copyright (C) 2015 Freescale Semiconductor, Inc.

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License version 2 as

* published by the Free Software Foundation.

*/

/dts-v1/;

#include <dt-bindings/input/input.h>

#include "imx6ul.dtsi"

/ {

model = "Freescale i.MX6 UltraLite 14x14 EVK Board";

compatible = "fsl,imx6ul-14x14-evk", "fsl,imx6ul";

chosen {

stdout-path = &uart1;

};

memory {

reg = <0x80000000 0x10000000>;

};

//one wire gpio

onewire@0 {

compatible = "w1-gpio";

gpios = <&gpio4 19 GPIO_ACTIVE_HIGH>;

linux,open-drain;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_onewire>;

status = "okay";

};

//gpio backlight for evb-p6ul 17.03

/*

backlight {

compatible = "gpio-backlight";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_backlight>;

gpios = <&gpio5 9 GPIO_ACTIVE_HIGH>;

default-brightness-level = <1>;

default-on;

};

*/

/*

backlight { //pwm 注意pwm时钟源

compatible = "pwm-backlight";

pwms = <&pwm1 0 500000>;

brightness-levels = <0 4 8 16 32 64 128 255>;

default-brightness-level = <6>;

enable-gpios = <&gpio5 9 0>;

status = "okay";

};

*/

pxp_v4l2 {

compatible = "fsl,imx6ul-pxp-v4l2", "fsl,imx6sx-pxp-v4l2", "fsl,imx6sl-pxp-v4l2";

status = "okay";

};

regulators {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <0>;

reg_can_3v3: regulator@0 {

compatible = "regulator-fixed";

reg = <0>;

regulator-name = "can-3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

// gpios = <&gpio_spi 3 GPIO_ACTIVE_LOW>;

};

reg_sd1_vmmc: regulator@1 {

compatible = "regulator-fixed";

regulator-name = "VSD_3V3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio1 5 GPIO_ACTIVE_HIGH>;

enable-active-high;

};

/*EVB-P6UL otg1 is otg,otg2 is usb host*/

reg_usb_otg1_vbus: regulator@2 {

compatible = "regulator-fixed";

reg = <2>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usb_otg1>;

regulator-name = "usb_otg1_vbus";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

gpio = <&gpio1 4 GPIO_ACTIVE_HIGH>;

enable-active-high;

};

/*EVB-P6UL otg1 is otg,otg2 is usb host*/

reg_usb_otg2_vbus: regulator@3 {

compatible = "regulator-fixed";

reg = <3>;/*????????重新核查*/

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usb_otg2>;

regulator-name = "usb_otg2_vbus";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

gpio = <&gpio1 2 GPIO_ACTIVE_HIGH>;

enable-active-high;

};

/*

reg_gpio_dvfs: regulator-gpio {

compatible = "regulator-gpio";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_dvfs>;

regulator-min-microvolt = <1300000>;

regulator-max-microvolt = <1400000>;

regulator-name = "gpio_dvfs";

regulator-type = "voltage";

gpios = <&gpio5 3 GPIO_ACTIVE_HIGH>;

states = <1300000 0x1 1400000 0x0>;

};

*/

};

sound {

compatible = "fsl,imx6ul-evk-wm8960",

"fsl,imx-audio-wm8960";

model = "wm8960-audio";

cpu-dai = <&sai2>;

audio-codec = <&codec>;

asrc-controller = <&asrc>;

codec-master;

gpr = <&gpr>;

/*

* hp-det = <hp-det-pin hp-det-polarity>;

* hp-det-pin: JD1 JD2 or JD3

* hp-det-polarity = 0: hp detect high for headphone

* hp-det-polarity = 1: hp detect high for speaker

*/

hp-det = <3 0>;

hp-det-gpios = <&gpio5 4 0>;

audio-routing =

"Headset Jack", "HP_L",

"Headset Jack", "HP_R",

"Ext Spk", "SPK_LP",

"Ext Spk", "SPK_LN",

"Ext Spk", "SPK_RP",

"Ext Spk", "SPK_RN",

"LINPUT2", "Hp MIC",

"LINPUT3", "Hp MIC",

"RINPUT1", "Main MIC",

"RINPUT2", "Main MIC",

"Hp MIC", "MICB",

"Main MIC", "MICB",

"CPU-Playback", "ASRC-Playback",

"Playback", "CPU-Playback",

"ASRC-Capture", "CPU-Capture",

"CPU-Capture", "Capture";

};

spi4 {

compatible = "spi-gpio";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_spi4>;

pinctrl-assert-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;

status = "disabled";

gpio-sck = <&gpio5 11 0>;

gpio-mosi = <&gpio5 10 0>;

cs-gpios = <&gpio5 7 0>;

num-chipselects = <1>;

#address-cells = <1>;

#size-cells = <0>;

gpio_spi: gpio_spi@0 {

compatible = "fairchild,74hc595";

gpio-controller;

#gpio-cells = <2>;

reg = <0>;

registers-number = <1>;

/*add for EVB-P6UL embedall 2017/01/19

* CSI_PWDN --> Q0 (high active)

* CSI_nRST --> Q1 (low active)

* WIFI_nPWEN --> Q2 (low active)

* PCIE_nRST --> Q3 (low active)

* PCIE_nDIS --> Q4 (low active)

* BUZ_PWEN --> Q5 (high active)

* LED0_nPWREN --> Q6 (low active)

* LED1_nPWREN --> Q7 (low active)

*/

registers-default = /bits/ 8 <0xda>;

/*11011010 74hc595 default io state embedall 17/01/19*/

spi-max-frequency = <100000>;

};

};

/* buzzer: buzzer {

compatible = "buzzer";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_buzzer>;

gpios = <&gpio5 3 GPIO_ACTIVE_LOW>;

//active-low;

};

*/

i2c@5 {

compatible = "i2c-gpio";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c_gpio>;

gpios = <&gpio2 9 0 /* sda */

&gpio2 8 0 /* scl */

>;

i2c-gpio,sda-open-drain;

i2c-gpio,scl-open-drain;

i2c-gpio,delay-us = <2>; /* ~100 kHz */

#address-cells = <1>;

#size-cells = <0>;

rx8010@32 {

compatible = "epson,rx8010";

reg = <0x32>;

};

};

leds {

compatible = "gpio-leds";

user-led1 {

label = "d1";

gpios = <&gpio_spi 6 GPIO_ACTIVE_LOW>;

linux,default-trigger = "none";

default-state = "off";

};

user-led2 {

label = "system";

gpios = <&gpio_spi 7 GPIO_ACTIVE_LOW>;

linux,default-trigger = "heartbeat";

// default-state = "off";

};

};

};

&cpu0 {

arm-supply = <®_arm>;

soc-supply = <®_soc>;

// dc-supply = <®_gpio_dvfs>;

};

&clks {

assigned-clocks = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <786432000>;

};

/*

&csi {

status = "disabled";

port {

csi1_ep: endpoint {

remote-endpoint = <&ov5640_ep>;

};

};

};

*/

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

};

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <1>;

};

};

};

&fec2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet2>;

phy-mode = "rmii";

phy-handle = <ðphy1>;

status = "disabled";

};

&pwm1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pwm1>;

status = "disabled";

};

&flexcan1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan1>;

xceiver-supply = <®_can_3v3>;

status = "disabled";

};

&flexcan2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan2>;

xceiver-supply = <®_can_3v3>;

status = "disabled";

};

&gpc {

fsl,cpu_pupscr_sw2iso = <0x1>;

fsl,cpu_pupscr_sw = <0x0>;

fsl,cpu_pdnscr_iso2sw = <0x1>;

fsl,cpu_pdnscr_iso = <0x1>;

fsl,wdog-reset = <1>; /* watchdog select of reset source */

fsl,ldo-bypass = <0>; /* DCDC, ldo-enable */

};

/*

&lcdif {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lcdif_dat>;

// &pinctrl_lcdif_ctrl>;

display = <&display0>;

status = "disabled";

display0: display {

bits-per-pixel = <32>;

bus-width = <18>;

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <36000000>;

hactive = <800>;

vactive = <480>;

hfront-porch = <20>;

hback-porch = <40>;

hsync-len = <2>;

vback-porch = <32>;

vfront-porch = <11>;

vsync-len = <0x11>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <0>;

};

};

};

};

*/

&pxp {

status = "okay";

};

&sai2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sai2>;

assigned-clocks = <&clks IMX6UL_CLK_SAI2_SEL>,

<&clks IMX6UL_CLK_SAI2>;

assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <0>, <12288000>;

status = "okay";

};

/* CHANGE BY PING EAC-SYSTEMS 16.11

&tsc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_tsc>;

status = "disabled";

xnur-gpio = <&gpio1 3 0>;

measure_delay_time = <0xffff>;

pre_charge_time = <0xfff>;

};

*/

&uart1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart1>;

status = "okay";

};

&uart2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart2>;

fsl,uart-has-rtscts;

/* for DTE mode, add below change */

/* fsl,dte-mode; */

/* pinctrl-0 = <&pinctrl_uart2dte>; */

status = "disabled";

};

/*

&uart3 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart3>;

status = "disabled";

};

*/

&uart4 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart4>;

status = "disabled";

};

/* RS485 */

&uart5 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart5>;

status = "disabled";

};

&uart6 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart6>;

status = "disabled";

};

&uart7 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart7>;

status = "disabled";

};

&uart8 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart8>;

status = "disabled";

fsl,uart-has-rtscts;

};

&usbotg1 {

vbus-supply = <®_usb_otg1_vbus>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usb_otg1_id>;

srp-disable;

hnp-disable;

adp-disable;

status = "okay";

};

&usbotg2 {

vbus-supply = <®_usb_otg2_vbus>;

dr_mode = "host";

status = "okay";

};

&usdhc1 {

pinctrl-names = "default", "state_100mhz", "state_200mhz";

pinctrl-0 = <&pinctrl_usdhc1>;

pinctrl-1 = <&pinctrl_usdhc1_100mhz>;

pinctrl-2 = <&pinctrl_usdhc1_200mhz>;

cd-gpios = <&gpio1 19 0>;

keep-power-in-suspend;

enable-sdio-wakeup;

vmmc-supply = <®_sd1_vmmc>;

status = "okay";

};

&usdhc2 {

pinctrl-names = "default", "state_100mhz", "state_200mhz";

pinctrl-0 = <&pinctrl_usdhc2_8bit>;

pinctrl-1 = <&pinctrl_usdhc2_8bit_100mhz>;

pinctrl-2 = <&pinctrl_usdhc2_8bit_200mhz>;

keep-power-in-suspend;

no-1-8-v;

bus-width = <8>;

non-removable;

status = "okay";

};

/*

&usdhc2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc2>;

no-1-8-v;

keep-power-in-suspend;

enable-sdio-wakeup;

status = "okay";

};

*/

&gpmi {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_gpmi_nand_1>;

status = "disabled";

nand-on-flash-bbt;

};

&i2c1 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c1>;

status = "okay";

adv761x@4c {

compatible = "adv761x";

reg = <0x4c>;

};

adv761x@58 {

compatible = "adv761x";

reg = <0x58>;

};

adv761x@50 {

compatible = "adv761x";

reg = <0x50>;

};

adv761x@22 {

compatible = "adv761x";

reg = <0x22>;

};

adv761x@32 {

compatible = "adv761x";

reg = <0x32>;

};

adv761x@34 {

compatible = "adv761x";

reg = <0x34>;

};

adv761x@23 {

compatible = "adv761x";

reg = <0x23>;

};

adv761x@33 {

compatible = "adv761x";

reg = <0x33>;

};

adv761x@35 {

compatible = "adv761x";

reg = <0x35>;

};

adv761x@37 {

compatible = "adv761x";

reg = <0x37>;

};

adv761x@39 {

compatible = "adv761x";

reg = <0x39>;

};

};

&i2c2 {

clock_frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c2>;

status = "disabled";

codec: wm8960@1a {

compatible = "wlf,wm8960";

reg = <0x1a>;

clocks = <&clks IMX6UL_CLK_SAI2>;

clock-names = "mclk";

wlf,shared-lrclk;

};

eeprom:eeprom@50 {

compatible = "atmel,24c256";

reg = <0x50>;

pagesize = <64>;

};

};

&qspi {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_qspi>;

status = "disabled";

fsl,qspi-has-second-chip = <1>;

ddrsmp=<0>;

};

&ecspi1 {

fsl,spi-num-chipselects = <1>;

cs-gpios = <&gpio4 26 0>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi1_1 &pinctrl_ecspi1_cs_1>;

status = "okay";

spidev0: spi@0 {

compatible = "oled_spi";

reg = <0>; //spi 地址

spi-max-frequency = <54000000>; //spi 最大时钟频率

};

};

&ecspi2 {

fsl,spi-num-chipselects = <1>;

cs-gpios = <&gpio4 22 0>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi2_2 &pinctrl_ecspi2_cs_2>;

status = "okay";

mcu_fpga: spi@1 {

compatible = "mcu_fpga";

reg = <0>; //spi 地址

spi-max-frequency = <54000000>; //spi 最大时钟频率

};

};

&ecspi3 {

fsl,spi-num-chipselects = <1>;

cs-gpios = <&gpio1 20 0>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi3_3 &pinctrl_ecspi3_cs_3>;

status = "okay";

spidev2: spi@2 {

compatible = "config_fpga";

reg = <0>; //spi 地址

spi-max-frequency = <54000000>; //spi 最大时钟频率

};

};

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

/*MX6UL_PAD_LCD_RESET__WDOG1_WDOG_ANY 0x30b0 #qiou*/

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059 /* SD1 VSELECT */

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x17059 /* SD1 RESET */

MX6UL_PAD_GPIO1_IO05__GPIO1_IO05 0x80000000 /* camera RESET*/

MX6UL_PAD_UART1_CTS_B__GPIO1_IO18 0x17059 /* usb hub RESET*/

//MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x17088 /*USBOTG1_ID */

//MX6UL_PAD_CSI_DATA07__GPIO4_IO28 0x80000000

>;

};

pinctrl_csi1: csi1grp {

fsl,pins = <

// MX6UL_PAD_CSI_MCLK__CSI_MCLK 0x1b088

// MX6UL_PAD_CSI_PIXCLK__CSI_PIXCLK 0x1b088

// MX6UL_PAD_CSI_VSYNC__CSI_VSYNC 0x1b088

// MX6UL_PAD_CSI_HSYNC__CSI_HSYNC 0x1b088

MX6UL_PAD_CSI_DATA00__CSI_DATA02 0x1b088

MX6UL_PAD_CSI_DATA01__CSI_DATA03 0x1b088

MX6UL_PAD_CSI_DATA02__CSI_DATA04 0x1b088

MX6UL_PAD_CSI_DATA03__CSI_DATA05 0x1b088

MX6UL_PAD_CSI_DATA04__CSI_DATA06 0x1b088

MX6UL_PAD_CSI_DATA05__CSI_DATA07 0x1b088

MX6UL_PAD_CSI_DATA06__CSI_DATA08 0x1b088

MX6UL_PAD_CSI_DATA07__CSI_DATA09 0x1b088

>;

};

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO07__ENET1_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET1_MDIO 0x1b0b0

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

// MX6UL_PAD_SNVS_TAMPER5__GPIO5_IO05 0x80000000

>;

};

pinctrl_enet2: enet2grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO07__ENET2_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET2_MDIO 0x1b0b0

MX6UL_PAD_ENET2_RX_EN__ENET2_RX_EN 0x1b0b0

MX6UL_PAD_ENET2_RX_ER__ENET2_RX_ER 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA0__ENET2_RDATA00 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA1__ENET2_RDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_EN__ENET2_TX_EN 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA0__ENET2_TDATA00 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA1__ENET2_TDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001b031

// MX6UL_PAD_SNVS_TAMPER6__GPIO5_IO06 0x80000000

>;

};

pinctrl_flexcan1: flexcan1grp{

fsl,pins = <

MX6UL_PAD_UART3_RTS_B__FLEXCAN1_RX 0x1b020

MX6UL_PAD_UART3_CTS_B__FLEXCAN1_TX 0x1b020

>;

};

pinctrl_flexcan2: flexcan2grp{

fsl,pins = <

MX6UL_PAD_UART2_RTS_B__FLEXCAN2_RX 0x1b020

MX6UL_PAD_UART2_CTS_B__FLEXCAN2_TX 0x1b020

>;

};

pinctrl_lcdif_dat: lcdifdatgrp {

fsl,pins = <

MX6UL_PAD_LCD_DATA00__LCDIF_DATA00 0x79

MX6UL_PAD_LCD_DATA01__LCDIF_DATA01 0x79

MX6UL_PAD_LCD_DATA02__LCDIF_DATA02 0x79

MX6UL_PAD_LCD_DATA03__LCDIF_DATA03 0x79

MX6UL_PAD_LCD_DATA04__LCDIF_DATA04 0x79

MX6UL_PAD_LCD_DATA05__LCDIF_DATA05 0x79

MX6UL_PAD_LCD_DATA06__LCDIF_DATA06 0x79

MX6UL_PAD_LCD_DATA07__LCDIF_DATA07 0x79

MX6UL_PAD_LCD_DATA08__LCDIF_DATA08 0x79

MX6UL_PAD_LCD_DATA09__LCDIF_DATA09 0x79

MX6UL_PAD_LCD_DATA10__LCDIF_DATA10 0x79

MX6UL_PAD_LCD_DATA11__LCDIF_DATA11 0x79

MX6UL_PAD_LCD_DATA12__LCDIF_DATA12 0x79

MX6UL_PAD_LCD_DATA13__LCDIF_DATA13 0x79

MX6UL_PAD_LCD_DATA14__LCDIF_DATA14 0x79

MX6UL_PAD_LCD_DATA15__LCDIF_DATA15 0x79

MX6UL_PAD_LCD_DATA16__LCDIF_DATA16 0x79

MX6UL_PAD_LCD_DATA17__LCDIF_DATA17 0x79

// MX6UL_PAD_LCD_DATA18__LCDIF_DATA18 0x79

// MX6UL_PAD_LCD_DATA19__LCDIF_DATA19 0x79

// MX6UL_PAD_LCD_DATA20__LCDIF_DATA20 0x79

// MX6UL_PAD_LCD_DATA21__LCDIF_DATA21 0x79

// MX6UL_PAD_LCD_DATA22__LCDIF_DATA22 0x79

// MX6UL_PAD_LCD_DATA23__LCDIF_DATA23 0x79

MX6UL_PAD_LCD_CLK__LCDIF_CLK 0x79

MX6UL_PAD_LCD_ENABLE__LCDIF_ENABLE 0x79

MX6UL_PAD_LCD_HSYNC__LCDIF_HSYNC 0x79

MX6UL_PAD_LCD_VSYNC__LCDIF_VSYNC 0x79

>;

};

pinctrl_pwm1: pwm1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO08__PWM1_OUT 0x79 //0x110b0 /*#qiou++ pwm test 0x110b0 0x79都可以? */

>;

};

pinctrl_lcdif_ctrl: lcdifctrlgrp {

fsl,pins = <

MX6UL_PAD_LCD_CLK__LCDIF_CLK 0x79

MX6UL_PAD_LCD_ENABLE__LCDIF_ENABLE 0x79

MX6UL_PAD_LCD_HSYNC__LCDIF_HSYNC 0x79

MX6UL_PAD_LCD_VSYNC__LCDIF_VSYNC 0x79

/* used for lcd reset */

//MX6UL_PAD_LCD_RESET__GPIO3_IO04 0x80000000

>;

};

pinctrl_uart1: uart1grp {

fsl,pins = <

MX6UL_PAD_UART1_TX_DATA__UART1_DCE_TX 0x1b0b1

MX6UL_PAD_UART1_RX_DATA__UART1_DCE_RX 0x1b0b1

>;

};

pinctrl_uart2: uart2grp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

//MX6UL_PAD_UART3_RX_DATA__UART2_DCE_RTS 0x1b0b1

//MX6UL_PAD_UART3_TX_DATA__UART2_DCE_CTS 0x1b0b1

>;

};

/*

pinctrl_uart2dte: uart2dtegrp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DTE_RX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DTE_TX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART2_DTE_CTS 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART2_DTE_RTS 0x1b0b1

>;

};

*/

/*

pinctrl_uart3: uart3grp {

fsl,pins = <

MX6UL_PAD_UART3_TX_DATA__UART3_DCE_TX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART3_DCE_RX 0x1b0b1

>;

};

*/

pinctrl_uart4: uart4grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__UART4_DCE_TX 0x1b0b1

MX6UL_PAD_UART4_RX_DATA__UART4_DCE_RX 0x1b0b1

>;

};

pinctrl_uart5: uart5grp {

fsl,pins = <

MX6UL_PAD_UART5_TX_DATA__UART5_DCE_TX 0x1b0b1

MX6UL_PAD_UART5_RX_DATA__UART5_DCE_RX 0x1b0b1

>;

};

pinctrl_uart6: uart6grp {

fsl,pins = <

MX6UL_PAD_ENET2_RX_DATA0__UART6_DCE_TX 0x1b0b1

MX6UL_PAD_ENET2_RX_DATA1__UART6_DCE_RX 0x1b0b1

>;

};

pinctrl_uart7: uart7grp {

fsl,pins = <

MX6UL_PAD_ENET2_RX_EN__UART7_DCE_TX 0x1b0b1

MX6UL_PAD_ENET2_TX_DATA0__UART7_DCE_RX 0x1b0b1

>;

};

pinctrl_uart8: uart8grp {

fsl,pins = <

MX6UL_PAD_ENET2_TX_DATA1__UART8_DCE_TX 0x1b0b1

MX6UL_PAD_ENET2_TX_EN__UART8_DCE_RX 0x1b0b1

MX6UL_PAD_ENET2_TX_CLK__UART8_DCE_CTS 0x1b0b1

MX6UL_PAD_ENET2_RX_ER__UART8_DCE_RTS 0x1b0b1

>;

};

pinctrl_usdhc1: usdhc1grp {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x17059

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x10071

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x17059

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x17059

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x17059

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x17059

>;

};

pinctrl_usdhc1_100mhz: usdhc1grp100mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170b9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100b9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170b9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170b9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170b9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170b9

>;

};

pinctrl_usdhc1_200mhz: usdhc1grp200mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170f9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100f9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170f9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170f9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170f9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170f9

>;

};

/*CoM-P6UL emmc boot USE USDHC2(8bit) EAC-SYSTEMS 17.01*/

pinctrl_usdhc2: usdhc2grp {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

>;

};

pinctrl_usdhc2_100mhz: usdhc2grp100mhz {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9

>;

};

pinctrl_usdhc2_200mhz: usdhc2grp200mhz {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9

>;

};

pinctrl_usdhc2_8bit: usdhc2_8bit_grp {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x17059

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x17059

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x17059

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x17059

>;

};

pinctrl_usdhc2_8bit_100mhz: usdhc2_8bit_100mhz_grp {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170b9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170b9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170b9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170b9

>;

};

pinctrl_usdhc2_8bit_200mhz: usdhc2_8bit_200mhz_grp {

fsl,pins = <

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170f9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170f9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170f9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170f9

>;

};

pinctrl_gpmi_nand_1: gpmi-nand-1 {

fsl,pins = <

MX6UL_PAD_NAND_CLE__RAWNAND_CLE 0xb0b1

MX6UL_PAD_NAND_ALE__RAWNAND_ALE 0xb0b1

MX6UL_PAD_NAND_WP_B__RAWNAND_WP_B 0xb0b1

MX6UL_PAD_NAND_READY_B__RAWNAND_READY_B 0xb000

MX6UL_PAD_NAND_CE0_B__RAWNAND_CE0_B 0xb0b1

MX6UL_PAD_NAND_CE1_B__RAWNAND_CE1_B 0xb0b1

MX6UL_PAD_NAND_RE_B__RAWNAND_RE_B 0xb0b1

MX6UL_PAD_NAND_WE_B__RAWNAND_WE_B 0xb0b1

MX6UL_PAD_NAND_DATA00__RAWNAND_DATA00 0xb0b1

MX6UL_PAD_NAND_DATA01__RAWNAND_DATA01 0xb0b1

MX6UL_PAD_NAND_DATA02__RAWNAND_DATA02 0xb0b1

MX6UL_PAD_NAND_DATA03__RAWNAND_DATA03 0xb0b1

MX6UL_PAD_NAND_DATA04__RAWNAND_DATA04 0xb0b1

MX6UL_PAD_NAND_DATA05__RAWNAND_DATA05 0xb0b1

MX6UL_PAD_NAND_DATA06__RAWNAND_DATA06 0xb0b1

MX6UL_PAD_NAND_DATA07__RAWNAND_DATA07 0xb0b1

>;

};

/* CoM-p6ul not use internal TSC

note by PING 16.11

pinctrl_tsc: tscgrp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0xb0

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0xb0

MX6UL_PAD_GPIO1_IO03__GPIO1_IO03 0xb0

MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0xb0

>;

};

*/

//ADD BY PING EAC-SYSTEMS 16.11

pinctrl_i2c1: i2c1grp {

fsl,pins = <

MX6UL_PAD_CSI_PIXCLK__I2C1_SCL 0x4001b8b0

MX6UL_PAD_CSI_MCLK__I2C1_SDA 0x4001b8b0

>;

};

/* EVB-P6UL USR UART4 FUNCTION

NOTE BY PING 16.11

pinctrl_i2c1: i2c1grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__I2C1_SCL 0x4001b8b0

MX6UL_PAD_UART4_RX_DATA__I2C1_SDA 0x4001b8b0

>;

};

*/

pinctrl_i2c2: i2c2grp {

fsl,pins = <

/*

MX6UL_PAD_UART5_TX_DATA__I2C2_SCL 0x4001f8a8

MX6UL_PAD_UART5_RX_DATA__I2C2_SDA 0x4001f8a8

*/

// MX6UL_PAD_CSI_HSYNC__I2C2_SCL 0x4001b8b0

// MX6UL_PAD_CSI_VSYNC__I2C2_SDA 0x4001b8b0

>;

};

//CoM-p6ul qspi nor flash boot note by PING 16.11

pinctrl_qspi: qspigrp {

fsl,pins = <

MX6UL_PAD_NAND_WP_B__QSPI_A_SCLK 0x70a1

MX6UL_PAD_NAND_READY_B__QSPI_A_DATA00 0x70a1

MX6UL_PAD_NAND_CE0_B__QSPI_A_DATA01 0x70a1

MX6UL_PAD_NAND_CE1_B__QSPI_A_DATA02 0x70a1

MX6UL_PAD_NAND_CLE__QSPI_A_DATA03 0x70a1

MX6UL_PAD_NAND_DQS__QSPI_A_SS0_B 0x70a1

MX6UL_PAD_NAND_DATA07__QSPI_A_SS1_B 0x70a1

MX6UL_PAD_NAND_RE_B__QSPI_B_SCLK 0x70a1

MX6UL_PAD_NAND_DATA02__QSPI_B_DATA00 0x70a1

MX6UL_PAD_NAND_DATA03__QSPI_B_DATA01 0x70a1

MX6UL_PAD_NAND_DATA04__QSPI_B_DATA02 0x70a1

MX6UL_PAD_NAND_DATA05__QSPI_B_DATA03 0x70a1

MX6UL_PAD_NAND_WE_B__QSPI_B_SS0_B 0x70a1

MX6UL_PAD_NAND_DATA00__QSPI_B_SS1_B 0x70a1

>;

};

pinctrl_sai2: sai2grp {

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

MX6UL_PAD_SNVS_TAMPER4__GPIO5_IO04 0x17059

>;

};

pinctrl_spi4: spi4grp {

fsl,pins = <

MX6UL_PAD_BOOT_MODE0__GPIO5_IO10 0x70a1

MX6UL_PAD_BOOT_MODE1__GPIO5_IO11 0x70a1

MX6UL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x70a1

MX6UL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x80000000

>;

};

//ADD BY VIC EAC-SYSTEMS 16.10

/* pinctrl_buzzer: buzzer {

fsl,pins = <

MX6UL_PAD_SNVS_TAMPER3__GPIO5_IO03 0x80000000

>;

};

*/

//ADD BY VIC EAC-SYSTEMS 16.10

pinctrl_ecspi1_cs_1: ecspi1_cs_grp-1 {

fsl,pins = <

MX6UL_PAD_CSI_DATA05__GPIO4_IO26 0x80000000

>;

};

//ADD BY VIC EAC-SYSTEMS 16.10

pinctrl_ecspi1_1: ecspi1grp-1 {

fsl,pins = <

MX6UL_PAD_CSI_DATA07__ECSPI1_MISO 0x10b0

MX6UL_PAD_CSI_DATA06__ECSPI1_MOSI 0x10b0

MX6UL_PAD_CSI_DATA04__ECSPI1_SCLK 0x10b0

>;

};

//ADD BY LINHAIBO

pinctrl_ecspi2_2: ecspi1grp-2 {

fsl,pins = <

MX6UL_PAD_CSI_DATA03__ECSPI2_MISO 0x10b0

MX6UL_PAD_CSI_DATA02__ECSPI2_MOSI 0x10b0

MX6UL_PAD_CSI_DATA00__ECSPI2_SCLK 0x10b0

>;

};

//ADD BY LINHAIBO

pinctrl_ecspi2_cs_2: ecspi2_cs_grp-2 {

fsl,pins = <

MX6UL_PAD_CSI_DATA01__GPIO4_IO22 0x80000000

>;

};

//ADD BY LINHAIBO

pinctrl_ecspi3_3: ecspi1grp-3 {

fsl,pins = <

MX6UL_PAD_UART2_RTS_B__ECSPI3_MISO 0x10b0

MX6UL_PAD_UART2_CTS_B__ECSPI3_MOSI 0x10b0

MX6UL_PAD_UART2_RX_DATA__ECSPI3_SCLK 0x10b0

>;

};

//ADD BY LINHAIBO

pinctrl_ecspi3_cs_3: ecspi3_cs_grp-3 {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__GPIO1_IO20 0x80000000

>;

};

//ADD BY VIC EAC-SYSTEMS 16.10

pinctrl_i2c_gpio: i2c_gpio {

fsl,pins = <

//MX6UL_PAD_SNVS_TAMPER5__GPIO5_IO05 0x4001b8b0

//MX6UL_PAD_SNVS_TAMPER6__GPIO5_IO06 0x4001b8b0

MX6UL_PAD_ENET2_RX_DATA1__GPIO2_IO09 0x4001b8b0

MX6UL_PAD_ENET2_RX_DATA0__GPIO2_IO08 0x4001b8b0

>;

};

/*add for EVB-P6UL usb otg1 2016/12/23*/

pinctrl_usb_otg1_id: usbotg1idgrp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x17059

>;

};

/*add for EVB-P6UL usb otg1 2016/12/23*/

pinctrl_usb_otg1: usbotg1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0x10b0

>;

};

/*add for EVB-P6UL usb otg2 to USB HOST 2016/12/23*/

pinctrl_usb_otg2: usbotg2grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0x10b0

>;

};

//add by vic eac-systems 16.11

pinctrl_edt_ft5x06: edt_ft5x06{

fsl,pins = <

MX6UL_PAD_SNVS_TAMPER0__GPIO5_IO00 0x80000000

MX6UL_PAD_SNVS_TAMPER1__GPIO5_IO01 0x80000000

>;

};

//add gpio backlight for evb-p6ul 17.03

/*

pinctrl_backlight: backlightgrp {

fsl,pins = <

MX6UL_PAD_SNVS_TAMPER9__GPIO5_IO09 0x4001b8b0

>;

};

*/

pinctrl_onewire: onewire@0 {

fsl,pins = <

MX6UL_PAD_CSI_VSYNC__GPIO4_IO19 0x4001b8b0

>;

};

};

};

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

On the same setup if you connect any other usb device ,is it detecting ?? can you try connecting USB having Hi & full speed and attach the log file ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

(1)usb host log :

# rmmod cx_usb_host.ko

usbcore: deregistering interface driver CX USB HOST

CX USB HOST 1-1.4:1.0: CX USB HOST #160 now disconnected

#

# insmod cx_usb_host.ko

CX USB HOST 1-1.4:1.0: CX USB HOST device now attached to USBSkel-160

usbcore: registered new interface driver CX USB HOST

(2)usb devcie log

# rmmod cx_usb_device.ko

# insmod cx_usb_device.ko

cx_usb_gadget gadget: CX_USB_Gadget, version: 2017 AUG 18

cx_usb_gadget gadget: cx_usb_gadget ready

# cx_usb_gadget gadget: high-speed config #1: cx_usb_gadget

cx_usb_gadget gadget: Using interface 0

(3)usb device plugged in usb host

# usb 1-1.4: USB disconnect, device number 4

CX USB HOST 1-1.4:1.0: CX USB HOST #160 now disconnected

usb 1-1.4: new high-speed USB device number 5 using ci_hdrc

CX USB HOST 1-1.4:1.0: CX USB HOST device now attached to USBSkel-160

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You didn't get what i asked i guess. I don't want .ko files snapshots. Please let me know on the same setup if you connect some other USB device is it detecting on the imx6ul processor in HOST mode?. Check lsusb and confirm whether usb detects with some other USB device

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

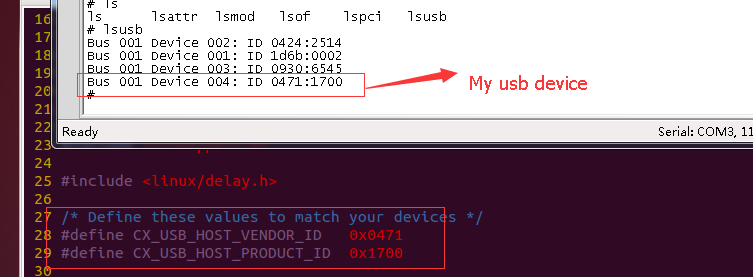

The usb device can be detected on the imx6ul processor in HOST mode . I am use lsusb can find my usb device , and can find some other USB device