- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- IMX6DQ DDR3 stress test failure

IMX6DQ DDR3 stress test failure

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I meet a problem that is ddr3 stress test failure like below

always failure at 64bit 's MSB 32bit write vlaue error。

ddr3 test script is "MX6Q_ARD_DDR3_register_programming_aid_v1.5.inc "

============================================

DDR Stress Test (2.6.0)

Build: Aug 1 2017, 17:33:25

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 Dual/Quad (0x63)

Internal Revision = TO1.2

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00021040

SRC_SBMR2(0x020d801c) = 0x12000001

============================================

ARM Clock set to 1GHz

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 15, col size: 10

Chip select CSD0 is used

Density per chip select: 2048MB

============================================

DDR Stress Test Iteration 1

Current Temperature: 46

============================================

DDR Freq: 528 MHz

t0.1: data is addr test

t0: memcpy10 SSN x64 test

Address of bank1 failure: 0x2182fec0

Data initially read was: 0xFFFFFEC4FFFFFFFF

Data re-read is: 0xFFFFFEC4FFFFFFFF

But pattern was: 0xFFFFFFFFFFFFFFFF

Error: failed to run stress test!!!

0x0 0x4 0x8 0xC

----------------------------------------------------------------------------------------------------------------

0x2182FEC0: 0xFFFFFFFF 0xFFFFFEC4 0x00001000 0x0000FECC

0x2182FED0: 0xFFFFFFFF 0xFFFFFED4 0x00002000 0x0000FEDC

0x2182FEE0: 0xFFFFFFFF 0xFFFFFEE4 0x00004000 0x0000FEEC

0x2182FEF0: 0xFFFFFFFF 0xFFFFFEF4 0x00008000 0x0000FEFC

0x2182FF00: 0xFFFFFFFF 0xFFFFFFFF 0x00010000 0x00000000

0x2182FF10: 0xFFFFFFFF 0xFFFFFFFF 0x00020000 0x00000000

0x2182FF20: 0xFFFFFFFF 0xFFFFFFFF 0x00040000 0x00000000

0x2182FF30: 0xFFFFFFFF 0xFFFFFFFF 0x00080000 0x00000000

memory read is done

Hardware:

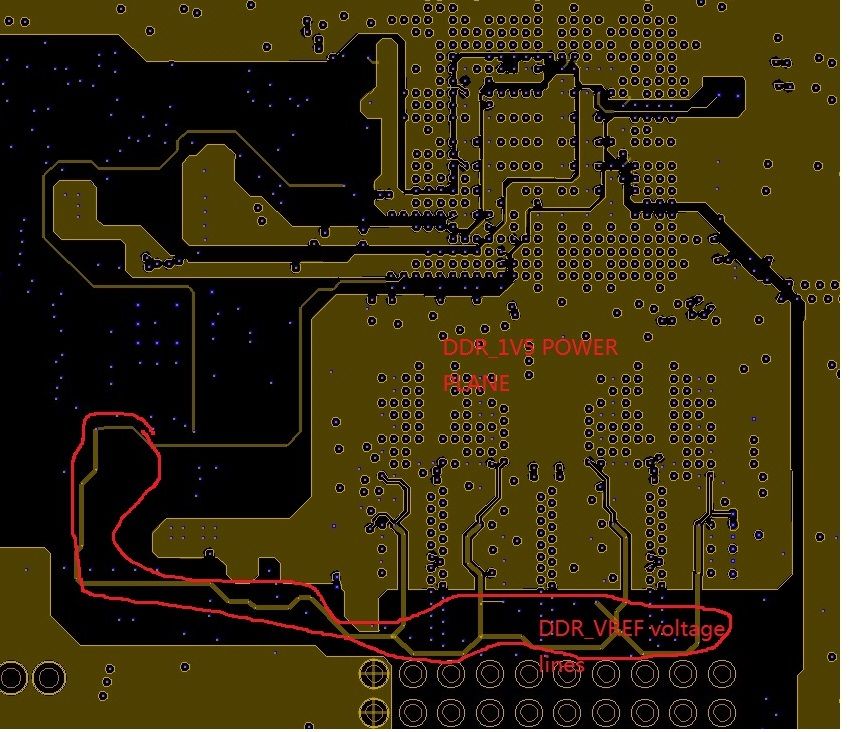

My design reference the sabre sdb 1GB ddr3 board。

ONLY change the ddr3 part number to fit the 2GB。“MT41K128M16JT-125 ” to “MT41K256M16HA-125IT”

The ddr3‘s signal route was same with the sabre sdb board 。

The sabre sdb use 8 layer layout, but I use 6 layer board layout to cost down and the DDR_VREF voltage use lines not plane。

Is this layout was poor,have any suggestion for me?

Can I fix this “ddr3’s stress test failure” problem by change the MMDC regs value?

or change the poor layout first?

Have any success IMX6DQ design use the 6 layers board before?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi yibo

such kind of errors may point to layout errors: broken or

connected together signal lines, one can check signals (in red) with

oscilloscope writing/reading problematic bit patterns with jtag.

May be recommended to recheck i.MX6 System Development User’s Guide

https://www.nxp.com/docs/en/user-guide/IMX6DQ6SDLHDG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi yibo

such kind of errors may point to layout errors: broken or

connected together signal lines, one can check signals (in red) with

oscilloscope writing/reading problematic bit patterns with jtag.

May be recommended to recheck i.MX6 System Development User’s Guide

https://www.nxp.com/docs/en/user-guide/IMX6DQ6SDLHDG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

But i am confusing with that the "data is addr test" was passed in stress testing. Is that can prove the hardware connection was right?

The value in red like addr that is the “data is addr test” step leave.

thanks for you reply. :smileyhappy: