- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hello All,

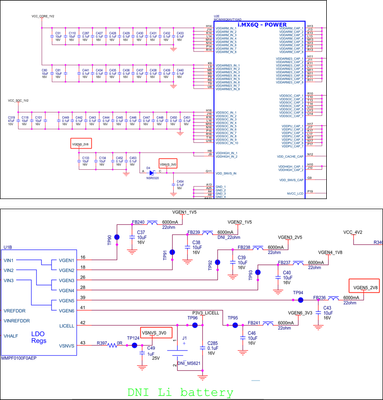

We have a custom board based on iMX6 quad core processor. It is designed to boot from eMMC.

Processor: IMX6 Quad, MCIMX6Q6AVT10AD

eMMC : IS21ES08G-JCLI

PMIC:MMPF0100F0AEP(Unconnected button battery)

Problem :

We see majority of boards boots as designed. But there are random failures on one or two boards per hundred( 1 to 2% only).When the startup fails, both SD3_CMD and SD3_CK remain high without any communication waveform.

Power supply design reference SCH-27516, VDDHIGH_IN is provided through PMIC GEN5, and VDD_SNVS_IN is provided through PMIC VSNVS.

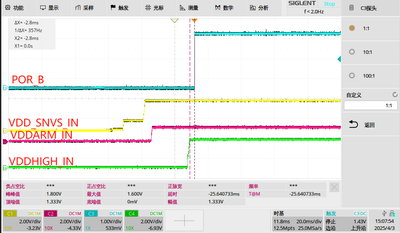

The following figure shows the power on timing sequence of the power supply

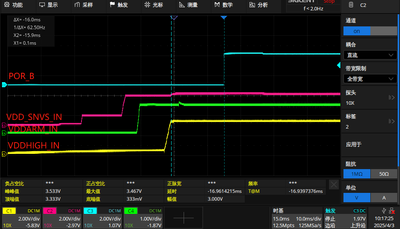

When we modified the design and changed VDDHIGH_IN from PMIC GEN5 to PMIC SW2, the issue of startup failure was resolved.

The following figure shows the modified power on sequence of the power supply

It can be observed that the time difference between VDDHIGH_IN and POR_B has increased from 2.8ms to 16ms.

Our question is:

1. Does VDDHIGH_IN have to be connected to VDD_SNVSIN without using button batteries

2. Does VDHIGH_IN have any power on sequence requirements relative to other power rails such as VDDARM_IN and VDDSOC_IN

3.Is there a time requirement for POR_B signal relative to VDDHIGH_IN, such as setting POR_B high after VDDHIGH_IN is ready for more than 5ms.

Looking forward to receiving a response to our questions, thank you!

已解决! 转到解答。