- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- How to setup EIM on iMX7 to emulate legacy INTEL bus

How to setup EIM on iMX7 to emulate legacy INTEL bus

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to setup EIM on iMX7 to emulate legacy INTEL bus

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sirs

I am looking for more information on how to setup and use the External Interface Module EIM on iMX7.

My need is to emulate legacy INTEL bus (AD0-AD15) (D0-D7) RD# WR# CS# ALE etc signals, using EIM module and signals.

Please is there any application note or similar examples on how to setup EIM control lines and control bus timing?

Thanks

Mario

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

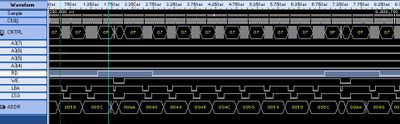

On the Logic Analyzer we detected 8 consecutive accesses on the memory region. The reference manual Figure 9-58 indicates that a single access should be done instead.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Would You please provide example of connection scheme i.MX7 (EIM) and

the external device?

Regards,

Yuri.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Mr Yuri

Thanks for your message!

Please find attached a schematics , simplified to show the concept.

Our goal is to use the iMX7 EIM module to directly interface to our legacy peripheral boards , all drive using old INTEL 8051 or 8096 controllers bus signals and timing.

We designed to use the IMX7 ALT4 configuration, where the EIM pins and register are in multiplexed mode.

In that way we need to emulate AD0-AD15 multiplexed address and data lines, as well RD# WR# ALE and CSx.

Note that we use the EIM-LBA_B signal as the ALE latch enable, and the EIM_OE as the RD# signal.

In the bus all A0-A15 was latched, and D0-D15 is the original AD0-AD15 multiplexed. Note the use of an external 74373 to latch address using LBA_B signal as ALE , going to external bus.

We need to generate the correct sequence and timing ALE CS WR/RD .

The attached schematics did not show the levels shifters, in sake of simplicity, but is necessary as the iMX7 is a 3.3V and the 8051 legacy bus 5V.

Please , inform if there is a application note or a more detailed guidelines on how to setup all EIM registers, and how to generate the correct timing on controls signals.

Thanks!

Mario Stefani

De: Yuri <admin@community.nxp.com>

Enviada em: quinta-feira, 16 de abril de 2020 23:55

Para: Mario A. Stefani <mario.stefani@opto.com.br>

Assunto: Re: - Re: How to setup EIM on iMX7 to emulate legacy INTEL bus

<https://community.freescale.com/resources/statics/1000/35400-NXP-Community-Email-banner-600x75.jpg> NXP Community

Re: How to setup EIM on iMX7 to emulate legacy INTEL bus

reply from Yuri Muhin <https://community.nxp.com/people/Yuri?et=watches.email.thread> in i.MX Processors - View the full discussion <https://community.nxp.com/message/1299603?commentID=1299603&et=watches.email.thread#comment-1299603>

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

We do not have app notes for the i.MX EIM, except, may be old app note AN2680

(EIM Asynchronous Timing Parameters), which may be used for i.MX7 only in general

sense.

https://www.nxp.com/docs/en/application-note/AN2680.pdf

Also section 9.7.7 (Typical Application) of the i.MX7 Reference Manual

(Rev. 1, 01/2018) provides useful examples.

As for our case, the Multiplexed Address/Data Mode should be used, as shown

in Table 44 (EIM internal module multiplexing) of the i.MX7 Datasheet (IMX7DCEC,

Rev. 6, 03/2019).

https://www.nxp.com/docs/en/data-sheet/IMX7DCEC.pdf

Regards,

Yuri.