- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Hardware design to using boundary scan test of i.MX7

Hardware design to using boundary scan test of i.MX7

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I use i.MX7 which is MCIMX7D3EVK10SD (12 x 12 mm) and I would like to use the Boundary scan test.

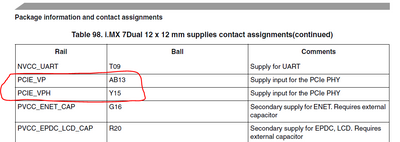

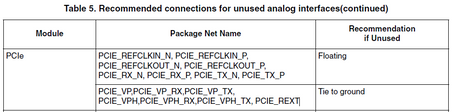

According to document "IMX7DSHDG" that mentioned as following.

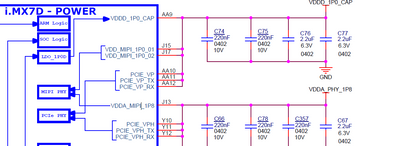

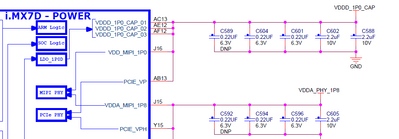

So, My hardware design will supply to PCI PHY, but MCIMX7D3EVK10SD has no PCIE_VPTX pin.

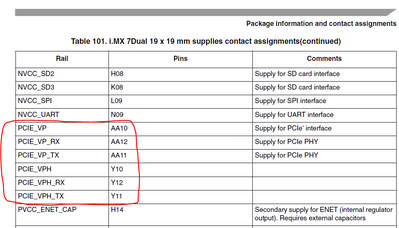

(MCIMX7D5EVM10SD(19 x 19 mm) has PCIE_VP pin , PCIE_VPH pin and PCIE_VPTX pin.)

Should I design to power supply to only PCIE_VP pin and PCIE_VPH pin?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

what do you mean MCIMX7D3EVK10SD has no PCIE_VPTX pin? do you mind sharing your connection about PCIE_VP pin and PCIE_VPH pin?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, @joanxie

According to Data sheet IMX7DCEC.pdf, in table 99 "iMX7Dual 12x12mm supplies contact...", there are PCIE_VP (AB13 Ball) and PCIE_VPH (Y15 Ball), but no PCIE_VP_TX.

On the other hand, table101 "iMX7Dual 19x19mm supplies contact...", There is PCIE_VP_TX (AA11 pins).

I use 12 x 12mm package. So that, I can not connect supply power to PCIE_VP_TX ball.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes, correct, you can compare the difference between them

19x19

12x12

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, @joanxie

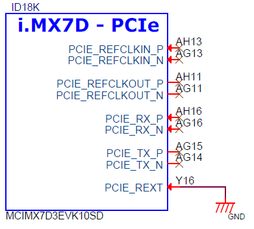

As per your reply, I intend to power supply to PCIE_VP and PCIE_VPH for using Boundary Scan.

I don't use PCIe function, in that case, should other PCIe signals (ex. PCIE_REXT) are connected to floating or tie to grand?

Should I follow the "Table 5 Recommended connections for unused analog interfaces" in "IMX7DCEC.pdf" excluding PCIE_VP and PCIE_VPH?

like below fig.?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

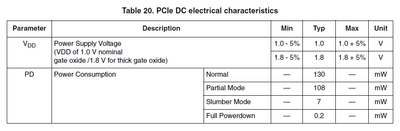

I attempt to power supply to PCIE_VP and PCIE_VPH for using Boundary Scan.

Although I don't use PCIE, Current consumption is up 70mA.

I guess I use MIPI, so that current consumption of PCIE up too.

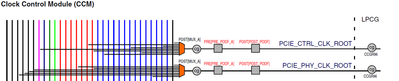

I set to disable PCIE_CTRL_CLK_ROOT and PCIE_PHY_CLK_ROOT of LPCG. But it has no effect on current consumption.

In that case, Are there other way to reduce the current consumption?

Would you teach me how to configure PCIe Full Powerdown mode?