- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Debugging U-boot on IMX6ULL using JTAG

Debugging U-boot on IMX6ULL using JTAG

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Debugging U-boot on IMX6ULL using JTAG

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

Trying to debug U-boot on IMX6ULL using this manual.

So I am able to compile U-boot sources using Eclipse and get binary U-boot file.

Enabled debugging options in .config file:

CONFIG_CC_OPTIMIZE_FOR_SIZE=n

CONFIG_TOOLS_DEBUG=y

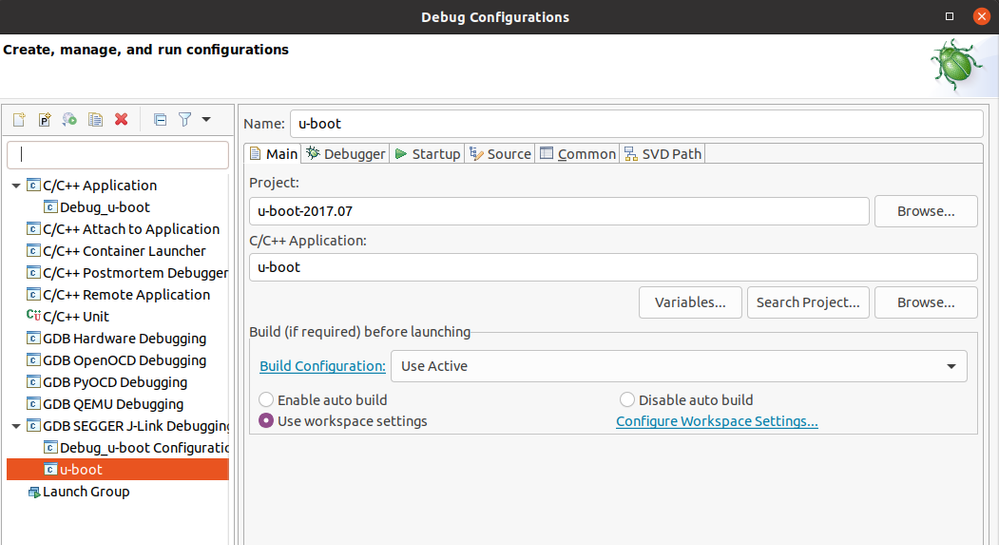

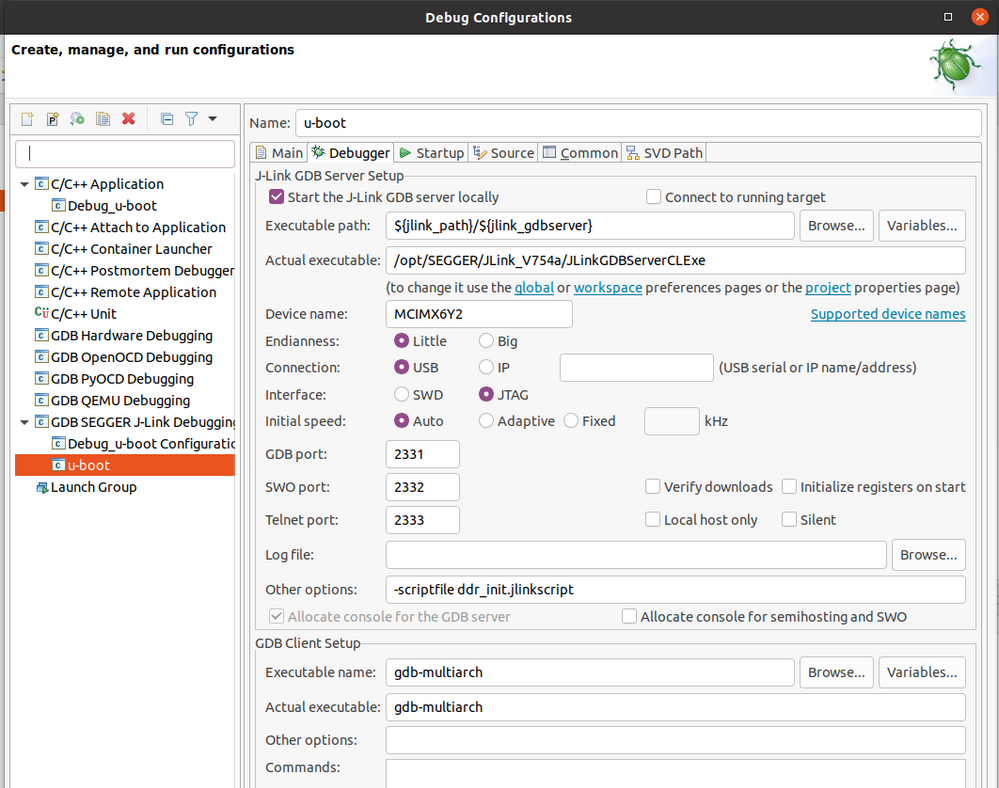

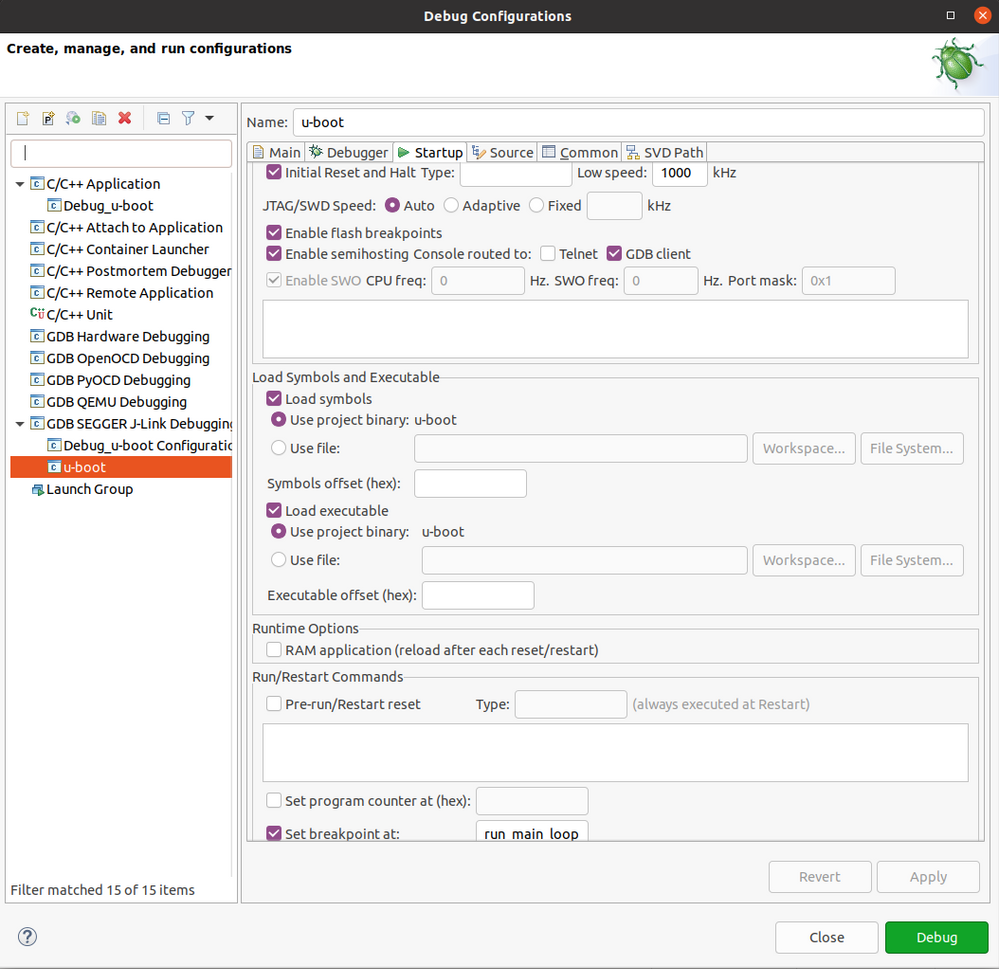

Here debugger configuration:

Get following logs on starting debugger server:

SEGGER J-Link GDB Server V7.54a Command Line Version

JLinkARM.dll V7.54a (DLL compiled Sep 7 2021 14:25:38)

Command line: -if jtag -device MCIMX6Y2 -endian little -speed auto -port 2331 -swoport 2332 -telnetport 2333 -noir -localhostonly 0 -scriptfile ddr_init.jlinkscript

-----GDB Server start settings-----

GDBInit file: none

GDB Server Listening port: 2331

SWO raw output listening port: 2332

Terminal I/O port: 2333

Accept remote connection: yes

Generate logfile: off

Verify download: off

Init regs on start: off

Silent mode: off

Single run mode: off

Target connection timeout: 0 ms

------J-Link related settings------

J-Link Host interface: USB

J-Link script: ddr_init.jlinkscript

J-Link settings file: none

------Target related settings------

Target device: MCIMX6Y2

Target interface: JTAG

Target interface speed: auto

Target endian: little

Connecting to J-Link...

J-Link is connected.

Firmware: J-Link ARM V8 compiled Nov 28 2014 13:44:46

Hardware: V8.00

Feature(s): RDI,FlashDL,FlashBP,JFlash,GDB

Checking target voltage...

Target voltage: 3.26 V

Listening on TCP/IP port 2331

Connecting to target...

J-Link found 3 JTAG devices, Total IRLen = 13

JTAG ID: 0x5BA00477 (Cortex-A7)

Connected to target

Waiting for GDB connection...Connected to 127.0.0.1

Reading all registers

Read 4 bytes @ address 0x87890988 (Data = 0x00000000)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F174 (Data = 0xEBFED7AE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F174 (Data = 0xEBFED7AE)

Read 2 bytes @ address 0x8785F178 (Data = 0xFFFE)

Read 2 bytes @ address 0x8785F176 (Data = 0xEBFE)

Read 2 bytes @ address 0x8785F174 (Data = 0xD7AE)

Read 2 bytes @ address 0x8785F178 (Data = 0xFFFE)

Read 2 bytes @ address 0x8785F176 (Data = 0xEBFE)

Read 2 bytes @ address 0x8785F174 (Data = 0xD7AE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F174 (Data = 0xEBFED7AE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F174 (Data = 0xEBFED7AE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Read 4 bytes @ address 0x8785F178 (Data = 0xEAFFFFFE)

Received monitor command: speed 1000

Target interface speed set to 1000 kHz

Received monitor command: clrbp

Received monitor command: reset

Resetting target

Received monitor command: halt

Halting target CPU...

...Target halted (PC = 0x8785F178)

Received monitor command: regs

PC = 8785F178, CPSR = 600001D3 (SVC mode, ARM FIQ dis. IRQ dis.)

R0 = 8785F180, R1 = 8786F6B8, R2 = 00000000, R3 = 0091F78D

R4 = 00000005, R5 = 87800320, R6 = 00000001, R7 = 8FF8D5BA

USR: R8 =8FF9CC8C, R9 =0091FA00, R10=8FF8D5BA, R11 =00000001, R12 =00000031

R13=80DB8C6B, R14=9E4F4394

FIQ: R8 =B6472704, R9 =846B1BF6, R10=DD3BACFE, R11 =EFF1EB7F, R12 =6E6C9283

R13=DC9247E9, R14=1F5A8FEF, SPSR=5A000312

SVC: R13=0091F9F0, R14=8785F178, SPSR=000001D3

ABT: R13=CDF44348, R14=6CA56019, SPSR=10038120

IRQ: R13=E966343D, R14=2AC8E2B6, SPSR=38026A20

UND: R13=7FC7CC2D, R14=11E13C9D, SPSR=20066601

Reading all registers

Received monitor command: speed auto

Select auto target interface speed (1000 kHz)

Received monitor command: flash breakpoints 1

Flash breakpoints enabled

Received monitor command: semihosting enable

Semi-hosting enabled (SVC Addr = 0x08)

Received monitor command: semihosting IOClient 2

Semihosting I/O set to GDB Client

Read 4 bytes @ address 0x87890988 (Data = 0x00000000)

Downloading 16272 bytes @ address 0x87800000

Downloading 16304 bytes @ address 0x87803F90

Downloading 16304 bytes @ address 0x87807F40

Downloading 16272 bytes @ address 0x8780BEF0

Downloading 16304 bytes @ address 0x8780FE80

Downloading 16272 bytes @ address 0x87813E30

Downloading 16288 bytes @ address 0x87817DC0

Downloading 16240 bytes @ address 0x8781BD60

Downloading 16272 bytes @ address 0x8781FCD0

Downloading 16272 bytes @ address 0x87823C60

Downloading 16256 bytes @ address 0x87827BF0

Downloading 16288 bytes @ address 0x8782BB70

Downloading 16272 bytes @ address 0x8782FB10

Downloading 16272 bytes @ address 0x87833AA0

Downloading 16256 bytes @ address 0x87837A30

Downloading 16256 bytes @ address 0x8783B9B0

Downloading 16256 bytes @ address 0x8783F930

Downloading 16304 bytes @ address 0x878438B0

Downloading 16288 bytes @ address 0x87847860

Downloading 16272 bytes @ address 0x8784B800

Downloading 16256 bytes @ address 0x8784F790

Downloading 16288 bytes @ address 0x87853710

Downloading 16160 bytes @ address 0x878576B0

Downloading 16192 bytes @ address 0x8785B5D0

Downloading 16272 bytes @ address 0x8785F510

Downloading 16272 bytes @ address 0x878634A0

Downloading 40 bytes @ address 0x87867430

Downloading 16120 bytes @ address 0x87867458

Downloading 16224 bytes @ address 0x8786B350

Downloading 16192 bytes @ address 0x8786F2B0

Downloading 16336 bytes @ address 0x878731F0

Downloading 16336 bytes @ address 0x878771C0

Downloading 1294 bytes @ address 0x8787B190

Downloading 24 bytes @ address 0x8787B6A0

Downloading 16328 bytes @ address 0x8787B6B8

Downloading 11484 bytes @ address 0x8787F680

Downloading 12 bytes @ address 0x8788235C

Downloading 4616 bytes @ address 0x87882368

Downloading 256 bytes @ address 0x87883570

Downloading 144 bytes @ address 0x87883670

Downloading 16256 bytes @ address 0x87883700

Downloading 16304 bytes @ address 0x87887680

Downloading 16304 bytes @ address 0x8788B630

Downloading 4928 bytes @ address 0x8788F5E0

Downloading 48 bytes @ address 0x87890920

Downloading 1 bytes @ address 0x87890950

Downloading 144 bytes @ address 0x87890954

Downloading 24 bytes @ address 0x878909E4

Writing register (PC = 0x87800000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 2 bytes @ address 0x87800000 (Data = 0x00B8)

Read 2 bytes @ address 0x877FFFFE (Data = 0x0000)

Read 2 bytes @ address 0x877FFFFC (Data = 0x0000)

Read 2 bytes @ address 0x87800000 (Data = 0x00B8)

Read 2 bytes @ address 0x877FFFFE (Data = 0x0000)

Read 2 bytes @ address 0x877FFFFC (Data = 0x0000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x8781503C (Data = 0xE52DE004)

Reading 64 bytes @ address 0x87817CC0

Read 4 bytes @ address 0x87817CD8 (Data = 0x8786811C)

Read 4 bytes @ address 0x87817CC8 (Data = 0xE59F0008)

Reading 64 bytes @ address 0x87818080

Read 4 bytes @ address 0x8781809C (Data = 0xE59F0004)

Reading 64 bytes @ address 0x87817E80

Read 4 bytes @ address 0x87817EA4 (Data = 0xEBFFF464)

Read 4 bytes @ address 0x87817EA0 (Data = 0xE92D4010)

Received monitor command: regs

PC = 87800000, CPSR = 600001D3 (SVC mode, ARM FIQ dis. IRQ dis.)

R0 = 8785F180, R1 = 8786F6B8, R2 = 00000000, R3 = 0091F78D

R4 = 00000005, R5 = 87800320, R6 = 00000001, R7 = 8FF8D5BA

USR: R8 =8FF9CC8C, R9 =0091FA00, R10=8FF8D5BA, R11 =00000001, R12 =00000031

R13=80DB8C6B, R14=9E4F4394

FIQ: R8 =B6472704, R9 =846B1BF6, R10=DD3BACFE, R11 =EFF1EB7F, R12 =6E6C9283

R13=DC9247E9, R14=1F5A8FEF, SPSR=5A000312

SVC: R13=0091F9F0, R14=8785F178, SPSR=000001D3

ABT: R13=CDF44348, R14=6CA56019, SPSR=10038120

IRQ: R13=E966343D, R14=2AC8E2B6, SPSR=38026A20

UND: R13=7FC7CC2D, R14=11E13C9D, SPSR=20066601

Reading all registers

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 2 bytes @ address 0x87800000 (Data = 0x00B8)

Read 2 bytes @ address 0x877FFFFE (Data = 0x0000)

Read 2 bytes @ address 0x877FFFFC (Data = 0x0000)

Read 2 bytes @ address 0x87800000 (Data = 0x00B8)

Read 2 bytes @ address 0x877FFFFE (Data = 0x0000)

Read 2 bytes @ address 0x877FFFFC (Data = 0x0000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x877FFFFC (Data = 0x00000000)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

Read 4 bytes @ address 0x87800000 (Data = 0xEA0000B8)

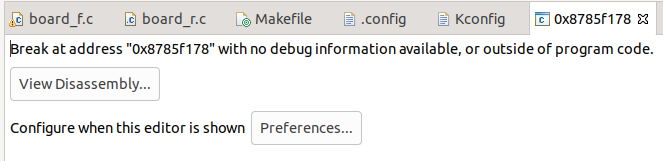

Everything looks fine but unfortunately get following error message at debugging window:

Another one thing confusing me is that u-boot console still accessible to enter commands and no reboot messages in console during startng debugging session.

Any hints what did I miss?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Almaz

may be useful below links

https://community.nxp.com/t5/i-MX-Processors-Knowledge-Base/Bring-up-i-MX6-via-JTAG/ta-p/1124954

https://forum.segger.com/index.php/Thread/5165-SOLVED-iMX6UL-DDR-initialization-for-u-boot/

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for links, Igor!

Checked them carefully. But still can't debug properly.

As there are troubles with Eclipse I decided to try from scratch, e.g. tried to debug from command line.

Here what I did.

Started JLinkGDBServer:

$ JLinkGDBServer -device MCIMX6Y2 -if JTAG -speed 1000with following logs:

SEGGER J-Link GDB Server V7.54a Command Line Version

JLinkARM.dll V7.54a (DLL compiled Sep 7 2021 14:25:38)

Command line: -device MCIMX6Y2 -if JTAG -speed 1000

-----GDB Server start settings-----

GDBInit file: none

GDB Server Listening port: 2331

SWO raw output listening port: 2332

Terminal I/O port: 2333

Accept remote connection: yes

Generate logfile: off

Verify download: off

Init regs on start: off

Silent mode: off

Single run mode: off

Target connection timeout: 0 ms

------J-Link related settings------

J-Link Host interface: USB

J-Link script: none

J-Link settings file: none

------Target related settings------

Target device: MCIMX6Y2

Target interface: JTAG

Target interface speed: 1000kHz

Target endian: little

Connecting to J-Link...

J-Link is connected.

Firmware: J-Link ARM V8 compiled Nov 28 2014 13:44:46

Hardware: V8.00

Feature(s): RDI,FlashDL,FlashBP,JFlash,GDB

Checking target voltage...

Target voltage: 3.26 V

Listening on TCP/IP port 2331

Connecting to target...

J-Link found 3 JTAG devices, Total IRLen = 13

JTAG ID: 0x5BA00477 (Cortex-A7)

Connected to target

Waiting for GDB connection...

then I created gdb init script based on lauterbach's dcd files and script provided there:

# Initializing target

target remote localhost:2331

monitor reset

monitor halt

monitor sleep 200

# Disable Watchdog

monitor memU32 0x020bc000=0x30

# Enable all clocks

monitor memU32 0x020c4068=0xffffffff

monitor memU32 0x020c406c=0xffffffff

monitor memU32 0x020c4070=0xffffffff

monitor memU32 0x020c4074=0xffffffff

monitor memU32 0x020c4078=0xffffffff

monitor memU32 0x020c407c=0xffffffff

monitor memU32 0x020c4080=0xffffffff

monitor memU32 0x020E04B4=0x000C0000

monitor memU32 0x020E04AC=0x00000000

monitor memU32 0x020E027C=0x00000030

monitor memU32 0x020E0250=0x00000030

monitor memU32 0x020E024C=0x00000030

monitor memU32 0x020E0490=0x00000030

monitor memU32 0x020E0288=0x000C0030

monitor memU32 0x020E0270=0x00000000

monitor memU32 0x020E0260=0x00000030

monitor memU32 0x020E0264=0x00000030

monitor memU32 0x020E04A0=0x00000030

monitor memU32 0x020E0494=0x00020000

monitor memU32 0x020E0280=0x00000030

monitor memU32 0x020E0284=0x00000030

monitor memU32 0x020E04B0=0x00020000

monitor memU32 0x020E0498=0x00000030

monitor memU32 0x020E04A4=0x00000030

monitor memU32 0x020E0244=0x00000030

monitor memU32 0x020E0248=0x00000030

monitor memU32 0x021B001C=0x00008000

monitor memU32 0x021B0800=0xA1390003

monitor memU32 0x021B080C=0x00000004

monitor memU32 0x021B083C=0x41640158

monitor memU32 0x021B0848=0x40403237

monitor memU32 0x021B0850=0x40403C33

monitor memU32 0x021B081C=0x33333333

monitor memU32 0x021B0820=0x33333333

monitor memU32 0x021B082C=0xf3333333

monitor memU32 0x021B0830=0xf3333333

monitor memU32 0x021B08C0=0x00944009

monitor memU32 0x021B08b8=0x00000800

monitor memU32 0x021B0004=0x0002002D

monitor memU32 0x021B0008=0x1B333030

monitor memU32 0x021B000C=0x676B52F3

monitor memU32 0x021B0010=0xB66D0B63

monitor memU32 0x021B0014=0x01FF00DB

monitor memU32 0x021B0018=0x00201740

monitor memU32 0x021B001C=0x00008000

monitor memU32 0x021B002C=0x000026D2

monitor memU32 0x021B0030=0x006B1023

monitor memU32 0x021B0040=0x0000004F

monitor memU32 0x021B0000=0x84180000

monitor memU32 0x021B0890=0x00400000

monitor memU32 0x021B001C=0x02008032

monitor memU32 0x021B001C=0x00008033

monitor memU32 0x021B001C=0x00048031

monitor memU32 0x021B001C=0x15208030

monitor memU32 0x021B001C=0x04008040

monitor memU32 0x021B0020=0x00000800

monitor memU32 0x021B0818=0x00000227

monitor memU32 0x021B0004=0x0002552D

monitor memU32 0x021B0404=0x00011006

monitor memU32 0x021B001C=0x00000000

monitor reg cpsr = 0xD3

monitor reg sp = 0x0093FF20

monitor reg pc = 0x87800000here is command I start gdb:

$ gdb-multiarch u-boot --nx -ix lauterbachand it outputs:

0x8ff62d00 in ?? ()

Resetting target

Sleep 200ms

Writing 0x00000030 @ address 0x020BC000

Writing 0xFFFFFFFF @ address 0x020C4068

Writing 0xFFFFFFFF @ address 0x020C406C

Writing 0xFFFFFFFF @ address 0x020C4070

Writing 0xFFFFFFFF @ address 0x020C4074

Writing 0xFFFFFFFF @ address 0x020C4078

Writing 0xFFFFFFFF @ address 0x020C407C

Writing 0xFFFFFFFF @ address 0x020C4080

Writing 0x000C0000 @ address 0x020E04B4

Writing 0x00000000 @ address 0x020E04AC

Writing 0x00000030 @ address 0x020E027C

Writing 0x00000030 @ address 0x020E0250

Writing 0x00000030 @ address 0x020E024C

Writing 0x00000030 @ address 0x020E0490

Writing 0x000C0030 @ address 0x020E0288

Writing 0x00000000 @ address 0x020E0270

Writing 0x00000030 @ address 0x020E0260

Writing 0x00000030 @ address 0x020E0264

Writing 0x00000030 @ address 0x020E04A0

Writing 0x00020000 @ address 0x020E0494

Writing 0x00000030 @ address 0x020E0280

Writing 0x00000030 @ address 0x020E0284

Writing 0x00020000 @ address 0x020E04B0

Writing 0x00000030 @ address 0x020E0498

Writing 0x00000030 @ address 0x020E04A4

Writing 0x00000030 @ address 0x020E0244

Writing 0x00000030 @ address 0x020E0248

Writing 0x00008000 @ address 0x021B001C

Writing 0xA1390003 @ address 0x021B0800

Writing 0x00000004 @ address 0x021B080C

Writing 0x41640158 @ address 0x021B083C

Writing 0x40403237 @ address 0x021B0848

Writing 0x40403C33 @ address 0x021B0850

Writing 0x33333333 @ address 0x021B081C

Writing 0x33333333 @ address 0x021B0820

Writing 0xF3333333 @ address 0x021B082C

Writing 0xF3333333 @ address 0x021B0830

Writing 0x00944009 @ address 0x021B08C0

Writing 0x00000800 @ address 0x021B08B8

Writing 0x0002002D @ address 0x021B0004

Writing 0x1B333030 @ address 0x021B0008

Writing 0x676B52F3 @ address 0x021B000C

Writing 0xB66D0B63 @ address 0x021B0010

Writing 0x01FF00DB @ address 0x021B0014

Writing 0x00201740 @ address 0x021B0018

Writing 0x00008000 @ address 0x021B001C

Writing 0x000026D2 @ address 0x021B002C

Writing 0x006B1023 @ address 0x021B0030

Writing 0x0000004F @ address 0x021B0040

Writing 0x84180000 @ address 0x021B0000

Writing 0x00400000 @ address 0x021B0890

Writing 0x02008032 @ address 0x021B001C

Writing 0x00008033 @ address 0x021B001C

Writing 0x00048031 @ address 0x021B001C

Writing 0x15208030 @ address 0x021B001C

Writing 0x04008040 @ address 0x021B001C

Writing 0x00000800 @ address 0x021B0020

Writing 0x00000227 @ address 0x021B0818

Writing 0x0002552D @ address 0x021B0004

Writing 0x00011006 @ address 0x021B0404

Writing 0x00000000 @ address 0x021B001C

Writing register (F0 = 0x000000D3)

Writing register (SP = 0x0093FF20)

Writing register (PC = 0x87800000)

Reading symbols from u-boot...then I:

(gdb) load

Loading section .text, size 0x67458 lma 0x87800000

Loading section .rodata, size 0x14246 lma 0x87867458

Loading section .hash, size 0x18 lma 0x8787b6a0

Loading section .data, size 0x6ca4 lma 0x8787b6b8

Loading section .got.plt, size 0xc lma 0x8788235c

Loading section .u_boot_list, size 0x1208 lma 0x87882368

Loading section .efi_runtime, size 0x100 lma 0x87883570

Loading section .efi_runtime_rel, size 0x90 lma 0x87883670

Loading section .rel.dyn, size 0xd220 lma 0x87883700

Loading section .dynsym, size 0x30 lma 0x87890920

Loading section .dynstr, size 0x1 lma 0x87890950

Loading section .dynamic, size 0x90 lma 0x87890954

Loading section .gnu.hash, size 0x18 lma 0x878909e4

Start address 0x87800000, load size 592375

Transfer rate: 718 KB/sec, 12341 bytes/write.and:

(gdb) s

Cannot access memory at address 0x87800000while gdb server:

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFE

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFE

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x877FFFFC

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x87800000

WARNING: Failed to read memory @ address 0x87800000Unable to access DDR memory.

After that I rebooted device, restarted GDB server using same command an started gdb in following way:

$ gdb-multiarch u-boot --nxand typed:

(gdb) target remote localhost:2331

Remote debugging using localhost:2331

0x8ff62d00 in ?? ()

(gdb) monitor reset

Resetting target

(gdb) monitor halt

(gdb) monitor sleep

Expected an decimal digit (0-9)

(gdb) monitor sleep 200

Sleep 200ms

(gdb) load

Loading section .text, size 0x67458 lma 0x87800000

Loading section .rodata, size 0x14246 lma 0x87867458

Loading section .hash, size 0x18 lma 0x8787b6a0

Loading section .data, size 0x6ca4 lma 0x8787b6b8

Loading section .got.plt, size 0xc lma 0x8788235c

Loading section .u_boot_list, size 0x1208 lma 0x87882368

Loading section .efi_runtime, size 0x100 lma 0x87883570

Loading section .efi_runtime_rel, size 0x90 lma 0x87883670

Loading section .rel.dyn, size 0xd220 lma 0x87883700

Loading section .dynsym, size 0x30 lma 0x87890920

Loading section .dynstr, size 0x1 lma 0x87890950

Loading section .dynamic, size 0x90 lma 0x87890954

Loading section .gnu.hash, size 0x18 lma 0x878909e4

Start address 0x87800000, load size 592375

Transfer rate: 69 KB/sec, 12341 bytes/write.Then:

(gdb) s

reset () at arch/arm/cpu/armv7/start.S:40

40 b save_boot_params

(gdb) s

save_boot_params () at arch/arm/cpu/armv7/start.S:116

116 b save_boot_params_ret @ back to my caller

(gdb) s

save_boot_params_ret () at arch/arm/cpu/armv7/start.S:56

56 mrs r0, cpsr

(gdb) s

57 and r1, r0, #0x1f @ mask mode bits

(gdb) s

58 teq r1, #0x1a @ test for HYP modelooks like I started to debug source code technically, but then:

Breakpoint 1 at 0x878020f4: file arch/arm/imx-common/cpu.c, line 184.

(gdb) c

Continuing.

s

c

^C

Program received signal SIGTRAP, Trace/breakpoint trap.

0x8785f178 in bootstage_error (id=BOOTSTAGE_ID_NEED_RESET) at include/bootstage.h:387

387 show_boot_progress(-id);E.g. it stuck somewhere until I pressed CTRL-C.

Repeated GdbServer and gdb restarting and passed same steps and it exited at another source code line.

So I repeated everything again and went step by step:

Start address 0x87800000, load size 592375

Transfer rate: 69 KB/sec, 12341 bytes/write.

(gdb) s

reset () at arch/arm/cpu/armv7/start.S:40

40 b save_boot_params

(gdb) s

save_boot_params () at arch/arm/cpu/armv7/start.S:116

116 b save_boot_params_ret @ back to my caller

(gdb)

save_boot_params_ret () at arch/arm/cpu/armv7/start.S:56

56 mrs r0, cpsr

(gdb)

57 and r1, r0, #0x1f @ mask mode bits

(gdb)

58 teq r1, #0x1a @ test for HYP mode

(gdb)

59 bicne r0, r0, #0x1f @ clear all mode bits

(gdb)

60 orrne r0, r0, #0x13 @ set SVC mode

(gdb) s

61 orr r0, r0, #0xc0 @ disable FIQ and IRQ

(gdb) s

62 msr cpsr,r0

(gdb) s

71 mrc p15, 0, r0, c1, c0, 0 @ Read CP15 SCTLR Register

(gdb) s

72 bic r0, #CR_V @ V = 0

(gdb) s

73 mcr p15, 0, r0, c1, c0, 0 @ Write CP15 SCTLR Register

(gdb) s

76 ldr r0, =_start

(gdb) s

77 mcr p15, 0, r0, c12, c0, 0 @Set VBAR

(gdb) s

82 bl cpu_init_cp15

(gdb) s

cpu_init_cp15 () at arch/arm/cpu/armv7/start.S:139

139 mov r0, #0 @ set up for MCR

(gdb) s

140 mcr p15, 0, r0, c8, c7, 0 @ invalidate TLBs

(gdb) s

141 mcr p15, 0, r0, c7, c5, 0 @ invalidate icache

(gdb) s

142 mcr p15, 0, r0, c7, c5, 6 @ invalidate BP array

(gdb) s

143 mcr p15, 0, r0, c7, c10, 4 @ DSB

(gdb) s

144 mcr p15, 0, r0, c7, c5, 4 @ ISB

(gdb) s

149 mrc p15, 0, r0, c1, c0, 0

(gdb) s

150 bic r0, r0, #0x00002000 @ clear bits 13 (--V-)

(gdb) s

151 bic r0, r0, #0x00000007 @ clear bits 2:0 (-CAM)

(gdb) s

152 orr r0, r0, #0x00000002 @ set bit 1 (--A-) Align

(gdb) s

153 orr r0, r0, #0x00000800 @ set bit 11 (Z---) BTB

(gdb) s

157 orr r0, r0, #0x00001000 @ set bit 12 (I) I-cache

(gdb) s

159 mcr p15, 0, r0, c1, c0, 0

(gdb) s

190 mov r5, lr @ Store my Caller

(gdb) s

191 mrc p15, 0, r1, c0, c0, 0 @ r1 has Read Main ID Register (MIDR)

(gdb) s

192 mov r3, r1, lsr #20 @ get variant field

(gdb) s

193 and r3, r3, #0xf @ r3 has CPU variant

(gdb) s

194 and r4, r1, #0xf @ r4 has CPU revision

(gdb) s

195 mov r2, r3, lsl #4 @ shift variant field for combined value

(gdb) s

196 orr r2, r4, r2 @ r2 has combined CPU variant + revision

(gdb) s

298 mov pc, r5 @ back to my caller

(gdb) s

save_boot_params_ret () at arch/arm/cpu/armv7/start.S:84

84 bl cpu_init_crit

(gdb) s

cpu_init_crit () at arch/arm/cpu/armv7/start.S:318

318 b lowlevel_init @ go setup pll,mux,memory

(gdb) s

lowlevel_init () at arch/arm/cpu/armv7/lowlevel_init.S:32

32 ldr sp, =CONFIG_SYS_INIT_SP_ADDR

(gdb) s

lowlevel_init () at arch/arm/cpu/armv7/lowlevel_init.S:34

34 bic sp, sp, #7 /* 8-byte alignment for ABI compliance */

(gdb) s

45 sub sp, sp, #GD_SIZE

(gdb) s

46 bic sp, sp, #7

(gdb) s

47 mov r9, sp

(gdb) s

53 push {ip, lr}

(gdb) s

68 bl s_init

(gdb)

s_init () at arch/arm/cpu/armv7/mx6/soc.c:588

588 if (is_mx6sx() || is_mx6ul() || is_mx6ull())

(gdb) s

get_cpu_rev () at arch/arm/cpu/armv7/mx6/soc.c:69

69 u32 reg = readl(&anatop->digprog_sololite);

(gdb) s

70 u32 type = ((reg >> 16) & 0xff);

(gdb)

73 if (type != MXC_CPU_MX6SL) {

(gdb)

74 reg = readl(&anatop->digprog);

(gdb)

76 cfg = readl(&scu->config) & 3;

(gdb)

77 type = ((reg >> 16) & 0xff);

(gdb)

76 cfg = readl(&scu->config) & 3;

(gdb)

78 if (type == MXC_CPU_MX6DL) {

(gdb)

83 if (type == MXC_CPU_MX6Q) {

(gdb)

89 major = ((reg >> So yeah, technically, I am able to debug U-boot but unable to pass first initialization procedures until any log message. But I am pretty sure that U-boot is correct as I am using it for a while!

Any ideas what is wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Then I did following:

(gdb) load

Loading section .text, size 0x67458 lma 0x87800000

Loading section .rodata, size 0x14246 lma 0x87867458

Loading section .hash, size 0x18 lma 0x8787b6a0

Loading section .data, size 0x6ca4 lma 0x8787b6b8

Loading section .got.plt, size 0xc lma 0x8788235c

Loading section .u_boot_list, size 0x1208 lma 0x87882368

Loading section .efi_runtime, size 0x100 lma 0x87883570

Loading section .efi_runtime_rel, size 0x90 lma 0x87883670

Loading section .rel.dyn, size 0xd220 lma 0x87883700

Loading section .dynsym, size 0x30 lma 0x87890920

Loading section .dynstr, size 0x1 lma 0x87890950

Loading section .dynamic, size 0x90 lma 0x87890954

Loading section .gnu.hash, size 0x18 lma 0x878909e4

Start address 0x87800000, load size 592375

Transfer rate: 69 KB/sec, 12341 bytes/write.

(gdb) s

reset () at arch/arm/cpu/armv7/start.S:40

40 b save_boot_params

(gdb) delete

(gdb) b initcall_run_list

Breakpoint 1 at 0x87856dec: file lib/initcall.c, line 17.

(gdb) s

save_boot_params () at arch/arm/cpu/armv7/start.S:116

116 b save_boot_params_ret @ back to my caller

(gdb) c

Continuing.

Breakpoint 1, initcall_run_list (init_sequence=init_sequence@entry=0x87870048 <init_sequence_f>) at lib/initcall.c:17

17 for (init_fnc_ptr = init_sequence; *init_fnc_ptr; ++init_fnc_ptr) {and yeah, I definitely debugging something but it fails on the early steps. Still can't understand what is wrong.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Almaz

suggest to post on segger forum.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Got it working. Prepared Docker image to get things easier. Thank you very much for your help!