- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- DDR stress test on IMX8QXP custom board and Evaluation board

DDR stress test on IMX8QXP custom board and Evaluation board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

DDR stress test on IMX8QXP custom board and Evaluation board

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Team.

Currently we have Si B0 part processor IMX8QXP-CPU EVK board but In EVK we are able to do DDR stress test and we are getting log also. Why we are not able to do DDR stress test in our custom board having Si B0 IMX8QXP processor.

Attached logs from EVK and Custom board. Kindly check and provide the steps further.

For Production we will use Si C0 revision processor part. Now we have to prove the working of this proto boards with Si B0. Please suggest to proceed further.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Could you tell us your customer board's difference between IMX8QXP-CPU EVK board ? Have customer change DDR?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In our custom board we are using same like as IMX8QXP_CPU design, Processor PIMX8QX6AVLFZAB is and LPDDR4 is part number is MT53E768M32D4DT-053AIT:E.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

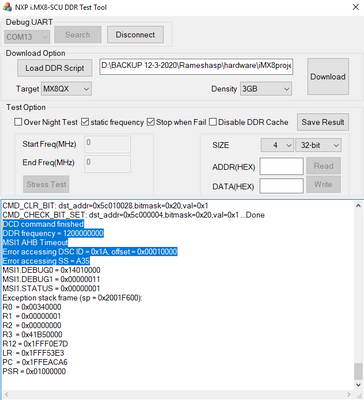

Also i am getting below error after running DDR script.

DCD command finished

DDR frequency = 1200000000

MSI1 AHB Timeout

Error accessing DSC ID = 0x1A, offset = 0x00010000

Error accessing SS = A35

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

How about the DDR frequency = 1600000000? You can try to change the DDR frequency to see if it can work

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no option to change DDR frequency to 1600000000, we can change only 800MHZ and 1200MHz.

Please suggest how to change DDR frequency to 1600000000.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

can you please provide some more information:

While doing DDR calibration I am getting in EVK board like below log.

*************************************************************************

MX8 DDR Stress Test Version: ER14

Built on Mar 27 2020 12:28:23

*************************************************************************

--Set up the MMU and enable I and D cache--

- This is the Cortex-A35 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x13d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x101122

- MMU and cache setup complete

*************************************************************************

ARM Clock(CA35): 1200MHz

DDR Clock: 1860MHz

============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 16, col size: 10

Two chip selects are used

Number of DDR controllers used on the SoC: 1

Density per chip select: 1536MB

Density per controller is: 3072MB

Total density detected on the board is: 3072MB

Command Bus Training was executed

********************************************

WARNING! DDR training errors were detected on DDRC 0!

DDR_PHY_PGSR0 = 0x8088c0ff

Write Leveling Adjustment training error detected

VREF training error detected

Recheck DDR initialization

********************************************

============================================

MX8QXP: Cortex-A35 is found

*************************************************************************

But in our custom board i am getting below log:

i.MX8QX_B0 is found

Download is complete

If you want to watch DDR script executing proces, please open SCU debug uart in other serial tool

Waiting for the target board boot...

can you please why i am not getting log as expected like EVK and what is the UART for Cortex-A35.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The aim of the DDR test tool is to find out the initial parameters of the LPDDR. The images built from the Yocto BSP is used for the EVK by default. So basically, you don't need to do the DDR test because you are using the same LPDDR4 as the EVK. You just need to modify the device tree file base on your board. Then the images build from Yocto should be able to boot on your board.