- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: DDR calibration issue on a custom iMX6Solo board

DDR calibration issue on a custom iMX6Solo board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to make DDR calibration on my custom iMX6 board. DDR memory chip is IS43TR16128B-125KBL.

I used MX6DL_SabreSD_DDR3_register_programming_aid_v2.2.xlsx as a reference to create registers settings.

For calibration I tried DDR_Stress_Tester_V1.0.2, DDR_Stress_Tester_V1.0.3 and ddr_stress_tester_v3.00

version 1.0.2 and 1.0.3 got the same result as in my comment

version 3.0.0 result:

============================================

DDR Stress Test (3.0.0)

Build: Dec 14 2018, 14:12:28

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 Solo/DualLite (0x61)

Internal Revision = TO1.3

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000000

SRC_SBMR2(0x020d801c) = 0x20000001

============================================

ARM Clock set to 800MHz

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 32, bank num: 8

Row size: 14, col size: 10

Chip select CSD0 is used

Density per chip select: 512MB

============================================

Current Temperature: 44

============================================

DDR Freq: 396 MHz

ddr_mr1=0x00000004

Start write leveling calibration...

running Write level HW calibration

MPWLHWERR register read out for factory diagnostics:

MPWLHWERR PHY0 = 0x00000000

HW WL cal status: no suitable delay value found for byte 0

HW WL cal status: no suitable delay value found for byte 1

HW WL cal status: no suitable delay value found for byte 2

HW WL cal status: no suitable delay value found for byte 3

Write leveling calibration completed but failed, the following results were found:

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x001F001F

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x001F001F

Write DQS delay result:

Write DQS0 delay: 31/256 CK

Write DQS1 delay: 31/256 CK

Write DQS2 delay: 31/256 CK

Write DQS3 delay: 31/256 CK

Error: failed during write leveling calibration

It is my first experience with iMX6 processors and DDR calibration.

My .xlsx file and DDR schematic are attached.

Thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found mistake in board assembling, incorrect value of C89 and C91 (signals DRAM_SDQS0 and DRAM_SDQS1)

After changing to correct value, board works as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I faced with the similar issue on our new board with imx6ULL and MT41K256M16TW-107.

One of our device with imx6ULL and MT41K256M16TW-107 works correctly.

But other one with the same imx6ULL and MT41K256M16TW-107 does not work.

Both devices DDR schematic are the same.

Here is voltage at power up:

+1V35_DRAM voltage is 1.35V

+VREF_DRAM voltage is 0.68V

R91 (SDCKE0) voltage is 0V

R92 (DRAM_RESET) voltage is 0V

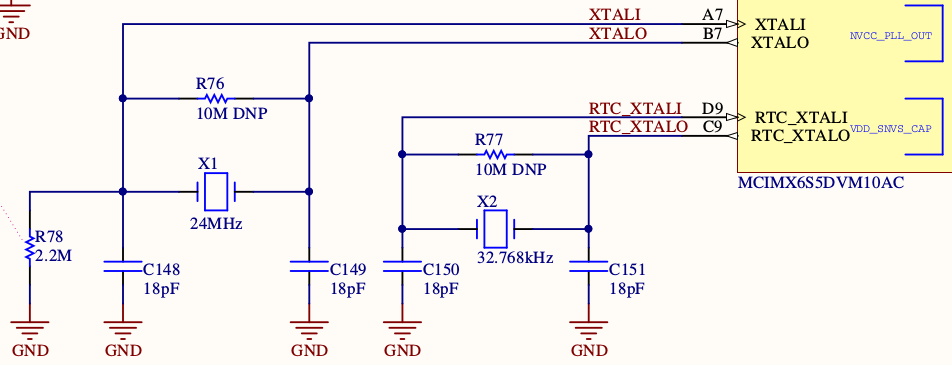

In our design we have 32kHz and 24MHz crystals. I checked both signals.

DDR Stress Test can not calibrate DDR, see log:

============================================

DDR Stress Test (3.0.0)

Build: Dec 14 2018, 14:13:23

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 UltraLiteLite(0x65)

Internal Revision = TO1.0

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000000

SRC_SBMR2(0x020d801c) = 0x00000001

============================================

ARM Clock set to 528MHz

============================================

DDR configuration

DDR type is DDR3

Data width: 16, bank num: 8

Row size: 15, col size: 10

Chip select CSD0 is used

Density per chip select: 512MB

============================================

Current Temperature: 45

============================================

DDR Freq: 396 MHz

ddr_mr1=0x00000000

Start write leveling calibration...

running Write level HW calibration

MPWLHWERR register read out for factory diagnostics:

MPWLHWERR PHY0 = 0x00000000

HW WL cal status: no suitable delay value found for byte 0

HW WL cal status: no suitable delay value found for byte 1

Write leveling calibration completed but failed, the following results were found:

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x001F001F

Write DQS delay result:

Write DQS0 delay: 31/256 CK

Write DQS1 delay: 31/256 CK

Error: failed during write leveling calibration

The log output is similar that I got early with imx6DL.

Can someone advise me what to check?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Found mistake in board assembling, incorrect value of C89 and C91 (signals DRAM_SDQS0 and DRAM_SDQS1)

After changing to correct value, board works as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

You have our latest stress test, that is good.

And what the test is telling you is that the board cannot even complete a Write Leveling routine, which requires the least amount of things to go wrong in order to complete.

There is something fundamentally wrong.

Have you confirmed that +1V5_DDR actually reads 1.5V?

Have you measured the +DDR_VREF voltage on C182? Does it read 0.75V?

What is the voltage on R81 (SDCKE0)?

What is the voltage on R82 (RESET_B)?

Is the layout in Allegro format? Would you be open in sharing it?

One last question: Does your design use a 32kHz crystal, or do you rely on the internal ring oscillator?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

Thanks for your help.

I can share DDR layout only next week.

+1V5_DDR voltage is 1.5V

+DDR_VREF voltage is 0.75V

R81 (SDCKE0) voltage is 0V

R82 (RESET_B) voltage is 0V

In our design we have 32kHz and 24MHz crystals.

I checked RESET_B signal on oscilloscope and found that is never goes to high so memory is always in reset state.

I have two assembled board and they have the same behavior.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

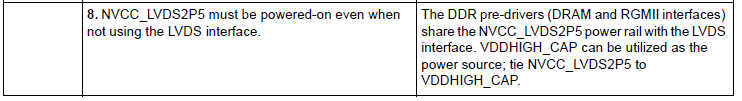

Found that NVCC_LVDS2P5 is required for DDR controller on iMX6, in our design it is off.

I think it will fix our issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

Yes, without power to the pre-drivers, the DDR pins don't work.

This is documented in the HWDG:

If you have to redesign the board in order to fix this problem, I would highly recommend downloading the HWDG from the NXP website and go through the checklist to make sure you don't get hit up with any other gotcha's.

i.MX 6Solo Applications Processors | Single Arm® Cortex®-A9 @ 1GHz | NXP

Cheers,

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I fix power issues on my board and DDR calibration and tests passed successfully.

Thanks for help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

I'm happy you were able to fix your board so quickly.

Good luck with your project.

Cheers,

Mark