- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Could not configure CSI0 bt.1120 on i.MX6Q

Could not configure CSI0 bt.1120 on i.MX6Q

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Could not configure CSI0 bt.1120 on i.MX6Q

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is a camera with LVDS output connected to the THC63LVD1024 converter (1080p30 video format). The chip is connected to CSI0, Y to D12 ~ D19, CbCr to D2 ~ D9, using DATA_EN, VSYNC, HSYNC, PIXCLOCK.

The device tree is configured as follows:

pinctrl_ipu1_csi0: ipu1csi0grp { /* parallel camera */

fsl,pins = <

MX6QDL_PAD_EIM_D27__IPU1_CSI0_DATA00 PAD_CTRL_HYS_PD

MX6QDL_PAD_EIM_D26__IPU1_CSI0_DATA01 PAD_CTRL_HYS_PD

MX6QDL_PAD_EIM_D31__IPU1_CSI0_DATA02 0xb0b1

MX6QDL_PAD_EIM_D30__IPU1_CSI0_DATA03 0xb0b1

MX6QDL_PAD_CSI0_DAT4__IPU1_CSI0_DATA04 0xb0b1

MX6QDL_PAD_CSI0_DAT5__IPU1_CSI0_DATA05 0xb0b1

MX6QDL_PAD_CSI0_DAT6__IPU1_CSI0_DATA06 0xb0b

MX6QDL_PAD_CSI0_DAT7__IPU1_CSI0_DATA07 0xb0b1

MX6QDL_PAD_CSI0_DAT8__IPU1_CSI0_DATA08 0xb0b1

MX6QDL_PAD_CSI0_DAT9__IPU1_CSI0_DATA09 0xb0b1

MX6QDL_PAD_CSI0_DAT10__IPU1_CSI0_DATA10 PAD_CTRL_HYS_PD

MX6QDL_PAD_CSI0_DAT11__IPU1_CSI0_DATA11 PAD_CTRL_HYS_PD

MX6QDL_PAD_CSI0_DATA_EN__IPU1_CSI0_DATA_EN 0xb0b1

//=================================STANDARD===============================================

MX6QDL_PAD_CSI0_DAT12__IPU1_CSI0_DATA12 0xb0b1

MX6QDL_PAD_CSI0_DAT13__IPU1_CSI0_DATA13 0xb0b1

MX6QDL_PAD_CSI0_DAT14__IPU1_CSI0_DATA14 0xb0b1

MX6QDL_PAD_CSI0_DAT15__IPU1_CSI0_DATA15 0xb0b1

MX6QDL_PAD_CSI0_DAT16__IPU1_CSI0_DATA16 0xb0b1

MX6QDL_PAD_CSI0_DAT17__IPU1_CSI0_DATA17 0xb0b1

MX6QDL_PAD_CSI0_DAT18__IPU1_CSI0_DATA18 0xb0b1

MX6QDL_PAD_CSI0_DAT19__IPU1_CSI0_DATA19 0xb0b1

MX6QDL_PAD_CSI0_PIXCLK__IPU1_CSI0_PIXCLK 0xb0b1

MX6QDL_PAD_CSI0_MCLK__IPU1_CSI0_HSYNC 0xb0b1

MX6QDL_PAD_CSI0_VSYNC__IPU1_CSI0_VSYNC 0xb0b1

//===================================================================================

>;

};

The device is declared as follows:

thc63lvd1024: thc63lvd1024 {

compatible = "thc63lvd1024";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ipu1_csi0 &pinctrl_cam_mclk>;

status = "okay";

ipu_id = <0>;

csi_id = <0>;

mclk = <74250000>;

mclk_source = <0>;

};

And also the kernel files (attached) are edited, the patch was taken as a basis https://community.nxp.com/thread/314211

I tried to set CSI0 to bt.1120 mode. But I never managed to capture the video with gstreamer.

What am I doing wrong?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

is it typo for "ipu_id = <0>;csi_id = <0>;" ?pls check if you set IPU_CSI0_SENS_CONF correct or not, and as I known, THC63LVD1024 can work on bt565 mode, if you want to see this mode, you can check the link as below:

https://community.nxp.com/docs/DOC-97981

the patch you use is for old bsp version, maybe you need to change something for your own bsp, but I'm not sure.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

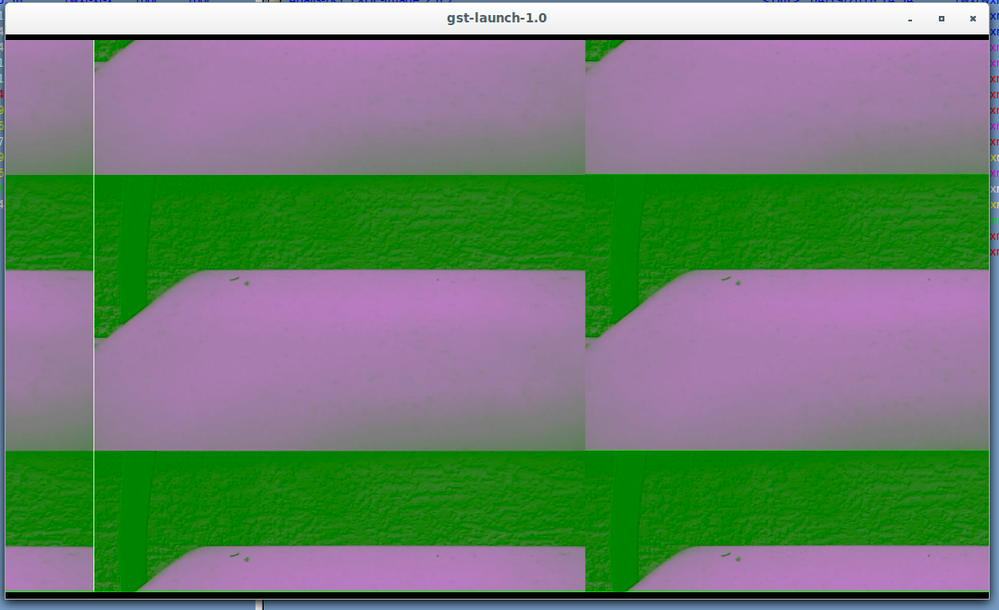

OK, I managed to get an image using the camera! It was necessary to turn off MX6QDL_PAD_CSI0_DATA_EN__IPU1_CSI0_DATA_EN to PAD_CTRL_HYS_PD . But now I have such an image (1080p30, V4L2_PIX_FMT_YUYV, IPU_CSI_DATA_WIDTH_8, IPU_CSI_CLK_MODE_GATED_CLK)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

it seems the de-interlacing issue, pls check this document as below:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

and I still do not understand what's wrong.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

you can check if you set correctly according to the application note I sent, and what mode do you use? bt1120 progressive mode? and what bsp version do you use?try to use mxc_v4l2_tvin.out to test first.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Joan Xie написал(а):

and what bsp version do you use?

Used apalis imx6 with the latest build 2.8.2

Joan Xie написал(а):

bt1120 progressive mode?

No, Gated Clock with Hsync, Vsync

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm not sure what 2.8.2 you mean, the latest bsp version for imx6q is 4.9.11, refer to the application note I sent to you, the chapter 2.7 Clock Mode Setting in Driver, That reference code used “clock_curr = 0” for BT.656/1120 interlaced clock mode; “clock_curr =1” for BT.656/1120 progressive clock mode; “clock_curr = others” for gated clock mode. pls check if you set this correct or not, and pls find more detailed information from this AN

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

is it typo for "ipu_id = <0>;csi_id = <0>;" ?

yes. corrected.

IPU_CSI0_SENS_CONF is configured as needed.

Sony 7520 camera is connected according to the diagram on page 64 (LVDS receiver circuit example (Double output)), datasheet attached.

may I need to use v4l2-dv-timings? because it already is a digital video. hmm