- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- CCM Output Generation

CCM Output Generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CCM Output Generation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I've been reading MX8MN RM for a while and try to figure out a way to generate CCM_CLKO at GPIO.

Also, I've read the following posts covering the CCM_CLKO topics

https://community.nxp.com/t5/i-MX-Processors/i-MX8MM-CCM-OUTPUT/td-p/1179744

https://community.nxp.com/t5/i-MX-Processors/clock-generation-on-CCM-CLKO2/m-p/628613

https://community.nxp.com/t5/i-MX-Processors/i-MX8M-Mini-definition-of-CCM-CLKO-2-1-pins/m-p/966969

https://community.nxp.com/t5/i-MX-Processors/CCM-CLKO-as-CLK-input-for-peripheral/m-p/971263

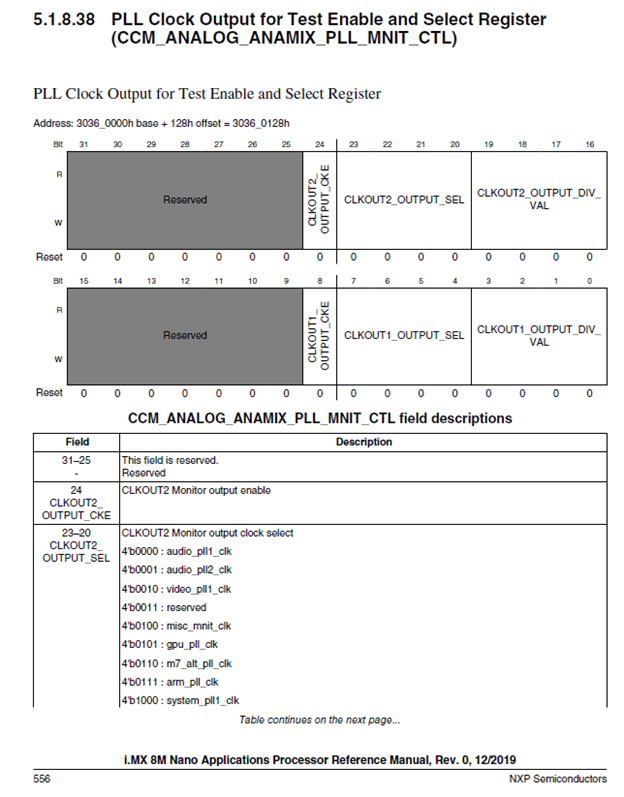

My first question is that MX8MN RM gives two different ways to configure CCM_CLKO.

1. Through CCM Mem Map Regs

CCM_CLKO locates in Slice 116/117 and can be accessed through CCM Mem Map Regs

2. Through CCM Analog Mem Map Regs

Which one should be use or what are the differences between these two register sets?

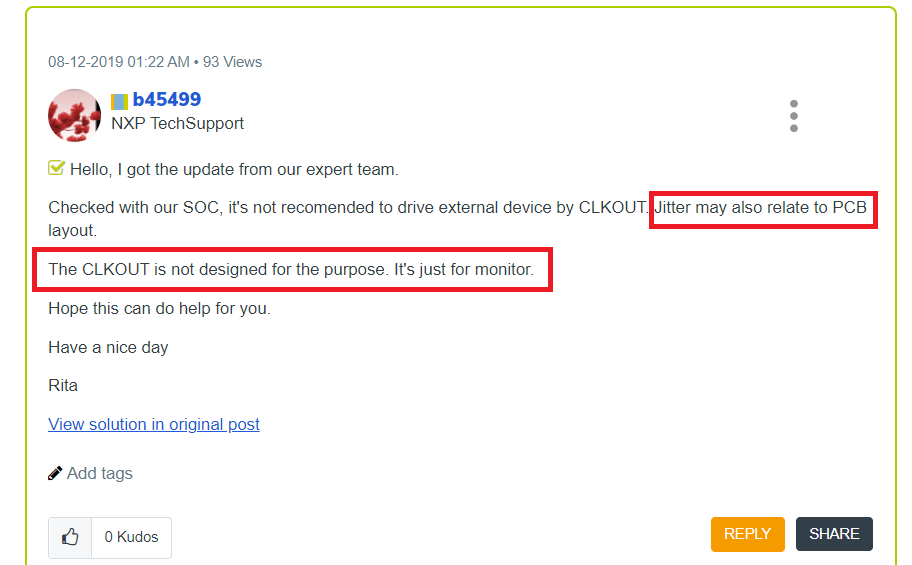

The second question is can I use a CLK buffer to deliver the CCM_CLKO to other peripherals?

In this post https://community.nxp.com/t5/i-MX-Processors/i-MX8MM-CCM-OUTPUT/td-p/1179744

Igor wrote that the stability is defined by the used crystal and it seems this CCM_CLKO can serve as a CLK source feeding other peripherals.

But in other posts,

https://community.nxp.com/t5/i-MX-Processors/CCM-CLKO-as-CLK-input-for-peripheral/m-p/971263

https://community.nxp.com/t5/i-MX-Processors/i-MX8M-Mini-definition-of-CCM-CLKO-2-1-pins/m-p/966969

guys were saying that CCM_CLO is just for monitor use.

So which saying is true?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi adam_smartind

>Which one should be use or what are the differences between these two register sets?

CCM_ANALOG_ANAMIX_PLL_MNIT_CTL should be used.

>The second question is can I use a CLK buffer to deliver the CCM_CLKO to other peripherals?

this depends on requirements of connected peripherals, strictly speaking CCM_CLKO was

not characterized for frequency stability and can not be used for very stable clock.

For example CLKO1 is used for camera on J802 connector p.11 SPF-31407 i.MX8M Nano Baseboard schematic

Design Files for the i.MX 8M Nano Evaluation Kit (8MNANOD4-EVK)

Best regards

igor