- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

Bt656 NTSC interlaced video support in imx6ull

Hi Team,

I am trying to get BT656 NTSC video(as per ITU BT.656-4 ) with imx6ull. I have few questions in this regard.

1. In the Refernce Manual, it is explained as CSI will put the field 1 and 2 back to back in the framebuffer, and from software , we have to recreate the original image, but in that it is also described as there is option to enable deinterlacing from the CSI .Could you please confirm whether deitnerlacing support is there in the imx6ull ?

2. In the mx6s_capture.c driver, for interlaced case, BASE ADDR SWITH EN bit is enabled. What is the necessitty of this particularly for interlaced video ?

3. As per BT656 standard (ITU BT.656-4) field0 has 244 active lines and field 1 243 active lines and there should be some option to skip these extra 7 lines to get actual 720x480 video. But in imx6ull how can we do this? if that can be done by using VSC field, how I can skip 7 lines ( 4 from field0 and 3 from fileld1) ? For imx6solo there were a IPU TV IN Application note which explains about this, but I couldn't find any doc for imx6ull. Please clarify this.

Hi abeeshmp_dct

>BASE ADDR SWITH EN bit is enabled. What is the necessitty of this

>particularly for interlaced video ?

for this question one can look at explanation on

Best regards

igor

Hi abeeshmp_dct

one can look at patches on

Best regards

igor

Hi igor,

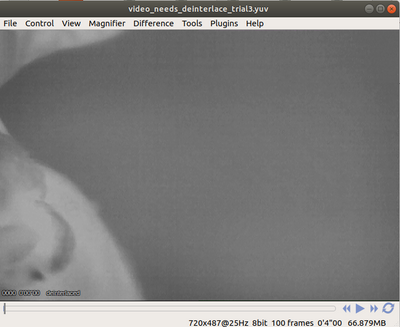

Thanks for the reply, I refered the same patch only, But I am getting vide as shown in below figure.

Note : The actual video file is attached for your reference

YUV image getting from v4l2 driver

If I deinterlace it using an external application( I used Vooya player in Linux PC), we will get actual frame as shown below,

after deitneralcing using an exrenal application

Please have you comment on this issue.

I have put asked 3 questions in first query, out of that first two are related to this, and last one is related to the line skip option, Please answer those questions. If question is not clear, please let me know.

Hi Igor,

I checked the link https://community.nxp.com/t5/i-MX-Processors/Fixing-base-address-switching-Change-Err-which-occurs-r...

But, there it explains about the Base adress switching error, I didn't find any answers for the necessity of base address switch enable for interlaced video , and also that discussoin is about csi-mipi. In my case, it is 8 bit parallel video.

Could you please help me to solve the issue I mentioned in last answer ( about deinterlacing)?

in interlaced video one buffer is used for even data, another for odd.

Discussion is about CSI module which is similar to i.MX6ULL, i.MX6SX.

Best regards

igor

Hi Igor,

As per the driver, we are giving two frame buffer's address to BUF1 and BUF2 base address registers and once we get the dma completion interrupt, then check for he BUF1 and BUF2 ineterrupt seperately and changes the corresponding base address registers accordingly,

So the DMA completion interrupt comes when we get the odd and even field contents into the frame buffer. And deitnerlacing is enabled and its stride is set from the driver for interlaced mode, I guess it is for the weaving method of data filling by the DMA for interacled mode.

And the critical thing is we are getting proper video with PAL format, the issue is with the NTSC video and from analysis, I guess it is due to some miss in configuratoin..

Did you have any information of testing NTSC video capture using the imx6ull CSI module ?

The FBUF_STRIDE means after DMA filled one line to target buffer, it can skip FBUF_STRIDE bytes to fill the next line to target buffer.

The use case can be followed:

Input camera video is 720*480, in normal case, you can use 720*480 size of buffer to capture it. Then FBUF_STRIDE is 0; and you can also use 1440*480 size of buffer to capture it and set FBUF_STRIDE to 720, then after captured one frame to the 1440*480 buffer, the left 720*480 of the 1440*480 buffer is the camera video.

The DEINTERLACE_STRIDE is similar as FBUF_STRIDE. In de-interlace mode, after received one line into target buffer, it will skip FBUF_STRIDE, the skip DEINTERLACE_STRIDE to save next line into target buffer.

For NTSC interlaced input from camera, we used 720*480 size of buffer to capture two 720*240 fields data, we cat set FBUF_STRIDE to 0 and DEINTERLACE_STRIDE to 720, so after received one line, the DMA will skip 720 words, then save to buffer again, so for first field, after received into target buffer, its data is in line 1, 3, 5, 7,....; and for second fields, its data will be save to target buffer line 2,4,6, 8,.....

Best regards

igor

Hi Igor,

Thanks for the detailed explanation.

On our case video input is as per ITU BT656-4 standard. We have used same video for imx6 based board and its working fine , we actually followed the steps mentioned in https://community.nxp.com/pwmxy87654/attachments/pwmxy87654/imx-processors%40tkb/5313/1/i.MX6_IPU_TV... for that case.

There we could use skip option to get 480 lines to buffer. But in case of imx6ull, we didn't find any guide like that.

So as per ITU-656-4 standard, there will be 244 lines for first field and 243 lined for second field.so do we need to have any extra configuration to get proper video for this standard.