- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Android 9 iMX8MM DDR4 Crash

Android 9 iMX8MM DDR4 Crash

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

RAM is MT40A512M16LY-075:E 2GB. I used MX8M_Mini_DDR4_RPA_v11 with ddr_tool_v3.10 for calibration and it passes without issue. I also ran an over-night test and had no problems. In u-boot I'm seeing the following <see below> when training is run. When compared to the evk the training points are different, the evk is using 2400 1D, 400 1D, 100 1D, and 2400 2D. Am I missing something when porting in the ddr4_timing.c from the DDR tool to u-boot imx_v2018.03_4.14.98_2.1.0?

SPL PMIC

pmic_reg_write(p, BD71837_BUCK1_VOLT_RUN, 0x0f);

pmic_reg_write(p, BD71837_BUCK2_VOLT_RUN, 0x0f);

/* increase VDD_DRAM to 0.975v for 3Ghz DDR */

pmic_reg_write(p, BD71837_BUCK5_VOLT, 0x83);

#ifndef CONFIG_IMX8M_LPDDR4

/* increase NVCC_DRAM_1V2 to 1.2v for DDR4 */

pmic_reg_write(p, BD71837_BUCK8_VOLT, 0x28);

#endif

Also calibrated with and without adjusting the PMIC from the ds file

sysparam set pmic_cfg 0x004b

sysparam set pmic_set 0x2f01 #REG_LOCK

sysparam set pmic_set 0x0d0f #BUCK1_VOLT_RUN 0.85v

sysparam set pmic_set 0x100f #BUCK2_VOLT_RUN 0.85v

sysparam set pmic_set 0x1483 #BUCK5_VOLT .975v

sysparam set pmic_set 0x1728 #BUCK8_VOLT 1.2v

sysparam set pmic_set 0x2f01 #REG_LOCK

I did have to add

busfreq {

status = "disabled";

}

to the device tree otherwise, the system would freeze.

U-Boot SPL 2018.03-dirty (Jul 06 2020 - 17:28:51 +0000)

power_bd71837_init

DDRINFO: start DRAM init

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 1336MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from USB SDP

Index 0 1

board_usb_init

struct dram_fsp_msg ddr_dram_fsp_msg[] = {

{

/* P0 2400mts 1D */

.drate = 2400,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp0_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_cfg),

},

{

/* P1 1336mts 1D */

.drate = 1336,

.fw_type = FW_1D_IMAGE,

.fsp_cfg = ddr_fsp1_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp1_cfg),

},

{

/* P0 2400mts 2D */

.drate = 2400,

.fw_type = FW_2D_IMAGE,

.fsp_cfg = ddr_fsp0_2d_cfg,

.fsp_cfg_num = ARRAY_SIZE(ddr_fsp0_2d_cfg),

},

};

[ 9.091097] Internal error: undefined instruction: 0 [#1] PREEMPT SMP

[ 9.097580] Modules linked in: wlan(+)

[ 9.101348] CPU: 2 PID: 3101 Comm: ip6tables-resto Not tainted 4.14.98-dirty #6

[ 9.108659] Hardware name: DCI i.MX8MM CBX3G board (DT)

[ 9.113886] task: ffff800073761c00 task.stack: ffff000013f10000

[ 9.119815] PC is at update_curr+0x30/0x224

[ 9.124003] LR is at dequeue_task_fair+0x6c/0x1068

[ 9.128794] pc : [<ffff000008114090>] lr : [<ffff000008117234>] pstate: 200001c5

[ 9.136191] sp : ffff000013f13af0

[ 9.139506] x29: ffff000013f13af0 x28: ffff80007ff97870

[ 9.144821] x27: ffff80007ff97800 x26: ffff0000098f4000

[ 9.150135] x25: ffff800073762250 x24: ffff80007ff97800

[ 9.155449] x23: ffff0000098f2018 x22: 0000000000000001

[ 9.160763] x21: ffff80007ff97870 x20: ffff80007ff97800

[ 9.166076] x19: ffff800073761c80 x18: 0000ffffe572a3ba

[ 9.171390] x17: 0000e450eb474188 x16: ffff00000829ec28

[ 9.176703] x15: 0000000000000006 x14: 00000000ffffffff

[ 9.182018] x13: 0000e450eae27680 x12: 0000e450eae27380

[ 9.187332] x11: 0000000000000000 x10: 0000000000000000

[ 9.192646] x9 : 00000000ffffffff x8 : 000000000000003f

[ 9.197960] x7 : 0000000000000000 x6 : 000000003eefbbb3

[ 9.203274] x5 : 000000021b6c8d5c x4 : 0000000000000000

[ 9.208588] x3 : 00000000000001c0 x2 : 0000000000005a9d

[ 9.213902] x1 : ffff800073761c00 x0 : 000000021b71d27b

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael

currently officially supported 2400/1066 i.MXM Mini ddr4 setpoints as in your tests.

Regarding 1336 - it is not supported for i.MXM Mini ddr4, I sent you additional material via mail.

In general one can tweak drive strength and ODT parameters in RPA tool.

Also may be recommended to try more new uboot releases as

imx_v2018.03_4.14.98_2.1.0 is very old.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael

> When compared to the evk the training points are different, the evk

>is using 2400 1D, 400 1D, 100 1D, and 2400 2D.

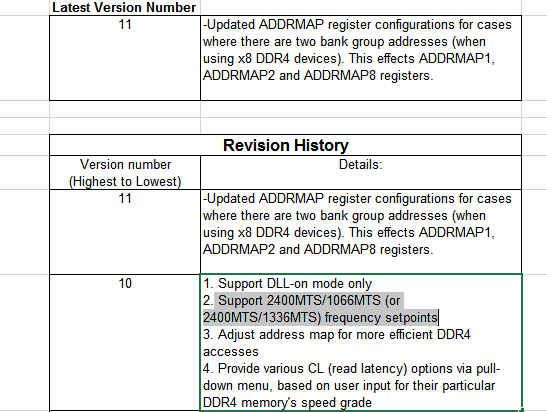

this is described in MX8M_Mini_DDR4_RPA_v11.xlsx Revision History

For training fail one can try to follow sect.4.3 Building u-boot image

MSCALE_DDR_Tool_User_Guide.pdf included in mscale_ddr_tool_v310_setup.exe.zip

sect.4.3.1 Building u-boot image by toolchain command..

Step3b. Replace DDR4 firmware and copy u-boot to imx_mkimage directory

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Igor. Unfortunately, I did replace the training binaries and copied the u-boot bins. I repeated the whole process just to confirm I did not miss anything, but I still have a training error.

625b90ed492425bec9c7fced37671c233a12d7bea9e050b72b2d62c8e7713aa5 iMX8M/ddr4_dmem_1d.bin

4cd3cd4340cc4aade5c1bacda3c6044b257838e543e613d93d6480317c3ad514 iMX8M/ddr4_dmem_2d.bin

6d65841d78bdd2d99df17e14fa4674b52111149d2161888e3c24527ac86d9591 iMX8M/ddr4_imem_1d.bin

3e24c256ec170f39bd85a7ab60dadb1ea47502dc272825a13135a1b5575ed5a3 iMX8M/ddr4_imem_2d.bin

1ee3ef869a748e7f11d36e359a8f1a773658d23ff74b841d97a3ac11c840a120 iMX8M/ddr4_train1d_string.bin

10a7bd10b76eb8efcb3994bcbd3a6b4032f8fb9b52ca2f4310128908c9382671 iMX8M/ddr4_train2d_string.bin

FIT description: Configuration to load ATF before U-Boot

Created: Fri Jul 10 13:10:49 2020

Image 0 (uboot@1)

Description: U-Boot (64-bit)

Created: Fri Jul 10 13:10:49 2020

Type: Standalone Program

Compression: uncompressed

Data Size: unavailable

Architecture: AArch64

Load Address: 0x40200000

Entry Point: unavailable

Image 1 (atf@1)

Description: ARM Trusted Firmware

Created: Fri Jul 10 13:10:49 2020

Type: Firmware

Compression: uncompressed

Data Size: unavailable

Architecture: AArch64

Load Address: 0x00920000

Image 2 (fdt@1)

Description: fsl-imx8mm-ddr4-val

Created: Fri Jul 10 13:10:49 2020

Type: Flat Device Tree

Compression: uncompressed

Data Size: unavailable

Compression: uncompressed [44/1793]

Data Size: unavailable

Architecture: Unknown Architecture

Default Configuration: 'config@1'

Configuration 0 (config@1)

Description: fsl-imx8mm-ddr4-val

Kernel: unavailable

FDT: fdt@1

Loadables: atf@1

./mkimage_imx8 -version v1 -fit -loader u-boot-spl-ddr4.bin 0x7E1000 -second_loader u-boot-ddr4.itb 0x40400000 0x60000 -out flash.bin

Platform: i.MX8M (mScale)

ROM VERSION: v1

Using FIT image

LOADER IMAGE: u-boot-spl-ddr4.bin start addr: 0x007e1000

SECOND LOADER IMAGE: u-boot-ddr4.itb start addr: 0x40400000 offset: 0x00060000

Output: flash.bin

========= IVT HEADER [HDMI FW] =========

header.tag: 0x0

header.length: 0x0

header.version: 0x0

entry: 0x0

reserved1: 0x0

dcd_ptr: 0x0

boot_data_ptr: 0x0

self: 0x0

csf: 0x0

reserved2: 0x0

boot_data.start: 0x0

boot_data.size: 0x0

boot_data.plugin: 0x0

========= IVT HEADER [PLUGIN] =========

header.tag: 0x0

header.length: 0x0

header.version: 0x0

entry: 0x0

reserved1: 0x0

dcd_ptr: 0x0

boot_data_ptr: 0x0

dcd_ptr: 0x0 [8/1793]

boot_data_ptr: 0x0

self: 0x0

csf: 0x0

reserved2: 0x0

boot_data.start: 0x0

boot_data.size: 0x0

boot_data.plugin: 0x0

========= IVT HEADER [LOADER IMAGE] =========

header.tag: 0xd1

header.length: 0x2000

header.version: 0x41

entry: 0x7e1000

reserved1: 0x57c00

dcd_ptr: 0x0

boot_data_ptr: 0x7e0fe0

self: 0x7e0fc0

csf: 0x80a5c0

reserved2: 0x0

boot_data.start: 0x7e0bc0

boot_data.size: 0x2ba00

boot_data.plugin: 0x0

========= OFFSET dump =========

Loader IMAGE:

header_image_off 0x0

dcd_off 0x0

image_off 0x40

csf_off 0x29600

spl hab block: 0x7e0fc0 0x0 0x29600

Second Loader IMAGE:

sld_header_off 0x57c00

sld_csf_off 0x58c20

sld hab block: 0x403fcdc0 0x57c00 0x1020

U-Boot SPL 2018.03-01210-gbfafde0-dirty (Jul 10 2020 - 13:10:31 -0500)

power_bd71837_init

DDRINFO: start DRAM init

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 1336MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

I calibrated and updated using 533 and then everything passed.

U-Boot SPL 2018.03-01210-gbfafde0-dirty (Jul 10 2020 - 13:57:00 -0500)

power_bd71837_init

DDRINFO: start DRAM init

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 1066MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 2400MTS

check ddr_pmu_train_imem code

check ddr_pmu_train_imem code pass

check ddr_pmu_train_dmem code

check ddr_pmu_train_dmem code pass

Training PASS

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from USB SDP

Index 0 1

board_usb_init

USB OTG Index 0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Michael

currently officially supported 2400/1066 i.MXM Mini ddr4 setpoints as in your tests.

Regarding 1336 - it is not supported for i.MXM Mini ddr4, I sent you additional material via mail.

In general one can tweak drive strength and ODT parameters in RPA tool.

Also may be recommended to try more new uboot releases as

imx_v2018.03_4.14.98_2.1.0 is very old.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Igor,

In the RPA excel file for the drive strength and ODT parameter, are only ATxImpedance, ODTImpedance and TxImpedance and modify?

Or other parameters can modify?

Best Regards

Chris Lin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes one can try to tweak these parameters,

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just an update. I corrected the BUCK2 to voltage to 1.0v, previously was 0.85v and the system now appears to be stable. However, I still do receive a training FAIL for 1336.

pmic_reg_write(p, BD71837_REGLOCK, 0x1);

/* increase VDD_SOC to typical value 0.85v before first DRAM access */

pmic_reg_write(p, BD71837_BUCK1_VOLT_RUN, 0x0f); //0.85v

pmic_reg_write(p, BD71837_BUCK2_VOLT_RUN, 0x1E); //1.0v

/* increase VDD_DRAM to 0.975v for 3Ghz DDR */

pmic_reg_write(p, BD71837_BUCK5_VOLT, 0x83);

#ifndef CONFIG_IMX8M_LPDDR4

/* increase NVCC_DRAM_1V2 to 1.2v for DDR4 */

pmic_reg_write(p, BD71837_BUCK8_VOLT, 0x28);

#endif