- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- Vybrid プロセッサ

- :

- Vybrid DCD DDR initialization

Vybrid DCD DDR initialization

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Everyone

Im trying to get a basic MQX project based on examples/hello booting from QSPI flash on Freescale Vybrid Tower module. I have succeeded booting it from QSPI flash and running the code from internal RAM, however now i want to get it working booting from QSPI in non XIP mode and running from the DDR memory instead, and im having problems initializing DDR inside the DCD structure.

I have tried to use the DDR init procedure from the \vf65gs10_a5_ddr.mac file converting it to DCD but without any success

I attach all the files to this post, any help will be greatly appreciated.

Thank you

Original Attachment has been moved to: quadspi_non_xip_DDR.icf.zip

Original Attachment has been moved to: quadspi_boot.h.txt.zip

Original Attachment has been moved to: quadspi_boot.c.txt.zip

Original Attachment has been moved to: vf65gs10_a5_ddr.mac.zip

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the helpful hints Jozef

I did manage to make it work. Im posting the working files to this thread in hopes someone might find it usefull.

To use the code attached, please make sure QSPI_DDR is defined somewhere.

Also, DCD_WRITE_CMD4 and DCD_CHECK_DATA_CMD4 macros are defined in quadspi_boot.h

ddr_init() in init_hw.c file in MQX bsp in deed should be commented out for the board to boot from QSPI flash.

As an interesting observation, in the ddr_init() there are several sleeps between the initializations of different ddr registers. When i tried to insert those sleeps in DCD using my DCD_DELAY_TICKS macro, board would not boot, however without them everything works fine. If anyone has any explanation for this please share

Thanks to everyone for the help

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Still trying to figure this out so Any help in regards to configuring and initializing DDR via DCD is greately appreciate. Sure someone had to do this already , any sample code will be highly appreciated .

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I guess you didn't try suppressing MQX DDR Init routine? ReInitializing DDR while executing code from it - it is like shooting into your own foot.

Did you also try connecting to target (after boot attempt) without reset and without debuggers DDR initialization steps to check if boot ROM succeeded initializing DDR and copying code from QSPI to DDR? In DS-5 debugger you may do so creating and using new "just connect" target.

If boot ROM succeeds initializing DDR and copying code but still no progress, also if suppressing DDR init doesn't help, then it looks like you need to debug your app from MQX entry point. Using DS-5 debugger you would need to create just connect target with right "load symbols from" setting, setting HW breakpoint at entry point, reset and hit continue button. Debugger should stop at HW breakpoint.

Hope this helps. I would try it myself, but my DS-5 license is over.

Edward

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Edward

I will try to disable MQX DDR init , great point, thank you ! I'm using IAR compiler but will try to locate similar settings as you have mentioned for ds5

Thanks again

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

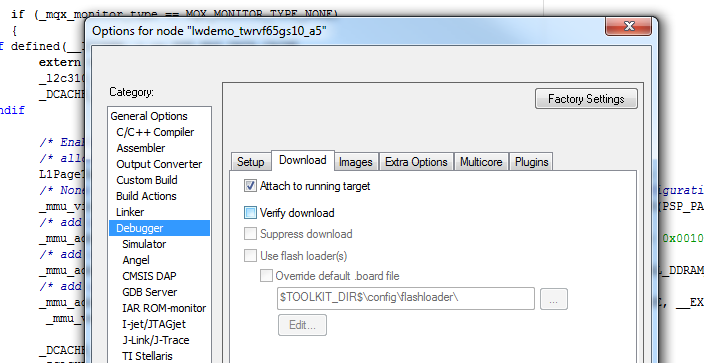

You can find attach to running target under Debugger options (in Project options):

As Ed mentions, do not forget disable DDR init in MQX (mqx\source\bsp\twrvf65gs10_a5\init_hw.c)

void init_hardware(void)

{

clocks_init();

// ddr_init();

_bsp_gpio_io_init();

}

Regards,

Jozef

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the helpful hints Jozef

I did manage to make it work. Im posting the working files to this thread in hopes someone might find it usefull.

To use the code attached, please make sure QSPI_DDR is defined somewhere.

Also, DCD_WRITE_CMD4 and DCD_CHECK_DATA_CMD4 macros are defined in quadspi_boot.h

ddr_init() in init_hw.c file in MQX bsp in deed should be commented out for the board to boot from QSPI flash.

As an interesting observation, in the ddr_init() there are several sleeps between the initializations of different ddr registers. When i tried to insert those sleeps in DCD using my DCD_DELAY_TICKS macro, board would not boot, however without them everything works fine. If anyone has any explanation for this please share

Thanks to everyone for the help

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I just found a little issue with my linker file, i attach the updated version that works when i just use it with the debugger, however QSPI boot into DDR still doesn't work.

/* Specials */

/* QSPI0 Linker Options */

define symbol __QSPI0_BASE_ADDRESS_START__ = 0x80000000;

define symbol __QSPI0_BASE_ADDRESS_END__ = 0x800ffff0;

/* Memory Regions */

define symbol __ICFEDIT_intvec_start__ = 0x80000800;

define symbol __ICFEDIT_region_ROM_start__ = 0x80000800;

define symbol __ICFEDIT_region_ROM_end__ = 0x800ffff0;

define symbol __ICFEDIT_region_RAM_start__ = 0x80200000;

define symbol __ICFEDIT_region_RAM_end__ = 0x87fffff0;

/* Sizes */

define symbol __ICFEDIT_size_bootstack__ = 0x100;

define symbol __ICFEDIT_size_sysstack__ = 0;

define symbol __ICFEDIT_size_fiqstack__ = 0;

define symbol __ICFEDIT_size_undstack__ = 0;

define symbol __ICFEDIT_size_abtstack__ = 0;

/* QSPI0 Configuration File Offset */

define symbol __QSPI0_CONF_OFFSET__ = __QSPI0_BASE_ADDRESS_START__ + 0x0;

define symbol __QSPI0_IVT_OFFSET__ = __QSPI0_BASE_ADDRESS_START__ + 0x400;

define symbol __QSPI0_BOOT_DATA_OFFSET__ = __QSPI0_BASE_ADDRESS_START__ + 0x420;

define symbol __QSPI0_DCD_OFFSET__ = __QSPI0_BASE_ADDRESS_START__ + 0x430;

define exported symbol __VECTOR_TABLE_ROM_START = 0x00000000;

define exported symbol __DEFAULT_PROCESSOR_NUMBER = 1;

/* 64kB of shared memory */

define exported symbol __SHARED_RAM_START = 0x3f040000;

define exported symbol __SHARED_RAM_END = 0x3f04fff0;

/* 62kB of sram pool */

define exported symbol __SRAM_POOL_START = 0x3f050000;

define exported symbol __SRAM_POOL_END = 0x3f07fbf0;

define exported symbol __UNCACHED_DATA_START = __SRAM_POOL_START;

define exported symbol __UNCACHED_DATA_END = __SRAM_POOL_END;

/* mem_init writes a storeblock_struct at the end of kernel data, max size 32 bytes */

define exported symbol __BOOT_STACK_ADDRESS = __ICFEDIT_region_RAM_end__ - __ICFEDIT_size_bootstack__;

define exported symbol __KERNEL_DATA_END = __ICFEDIT_region_RAM_end__;

define memory mem with size = 4G;

define region ROM_region = mem:[from __ICFEDIT_region_ROM_start__ to __ICFEDIT_region_ROM_end__];

define region RAM_region = mem:[from __ICFEDIT_region_RAM_start__ to __ICFEDIT_region_RAM_end__];

define block SYS_STACK with alignment = 8, size = __ICFEDIT_size_sysstack__ { };

define block FIQ_STACK with alignment = 8, size = __ICFEDIT_size_fiqstack__ { };

define block UND_STACK with alignment = 8, size = __ICFEDIT_size_undstack__ { };

define block ABT_STACK with alignment = 8, size = __ICFEDIT_size_abtstack__ { };

define block KERNEL_DATA with alignment = 32 { section .kernel_data };

define block VECTOR_TBL with alignment = 32 { section .vector_tbl };

define symbol CONF_OFFSET = __QSPI0_CONF_OFFSET__;

define symbol IVT_OFFSET = __QSPI0_IVT_OFFSET__;

define symbol BOOT_DATA_OFFSET = __QSPI0_BOOT_DATA_OFFSET__;

define symbol DCD_OFFSET = __QSPI0_DCD_OFFSET__;

initialize by copy { readwrite };

do not initialize { section .noinit };

do not initialize { section .kernel_data };

place at address mem:CONF_OFFSET { section .conf };

place at address mem:IVT_OFFSET { section .ivt };

place at address mem:BOOT_DATA_OFFSET { readonly section .boot_data };

place at address mem:DCD_OFFSET { readonly section .dcd };

keep{section .conf, section .ivt, section .boot_data, section .dcd};

place in ROM_region { first block head { section STARTUP }, readonly, block VECTOR_TBL };

place in RAM_region { readwrite, block SYS_STACK, block FIQ_STACK, block UND_STACK, block ABT_STACK, last block KERNEL_DATA };

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just wanted to add that im running MQX 4.1.1 on the A5 not the M4

thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

cyborgnegotiator can you review this case and share your thoughts?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Igor,

Before we proceed further, are you using our Tower board or your own design? - It is easier if ours whose hardware has been tested.

Based on your reply, I hope timesyssupport will be able to help you in the software part.

Regards, Naoum Gitnik.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Naoum,

User is running MQX on the Cortex-A5, We are providing support for Linux and MCC for the VF6xx processors, not MQX. Can the Freescale MQX team clarify the MQX questions that Igor has?

Thanks,

Timesys Support

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Naoum

Yes, im using the Tower board, however its an older one, the marking on the board is SCH-27442 Rev G

Marking on the CPU is Test Rev C3

thanks