- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Tシリーズ

- :

- Re: T1042 - DDR Controller Commad Signal Timings

T1042 - DDR Controller Commad Signal Timings

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

T1042 - DDR Controller Commad Signal Timings

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, We are trying to bringup DDR3L discrete RAMs on our custom board. We modified our RCW to set DDR clock frequency to 533MHz. We created a default QCVS DDR3 validation project and ran validation tests. All tests are failing by giving following errors:

Error configuring the target! - DDR initialization failed: D_INIT was not cleared by hardware

We verified signal routing, CLK, CKE and checked signals on probes on all command signals (RAS, CAS, WE, BA, Address etc.) used during DRAM init. However, we noticed two following abnormalities in the signals:

1. CKE was following init sequence but once it goes high it does not come to low (although CKE_PLS bits are set to use 4 clocks)

2. Command signals (we tested RAS and CAS) are being asserted for 3~4 clock cycles i.e 7~8 ns when running on 533MHz (although 1T timing is set in DDR controller settings). Please checkout the attached snapshot of RAS signal during init sequence.

Can someone confirm why T1042/DDR-controller is driving these signals with such behavior? Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Points to check:

1) RESET to the DDR SDRAM chips is applied correctly

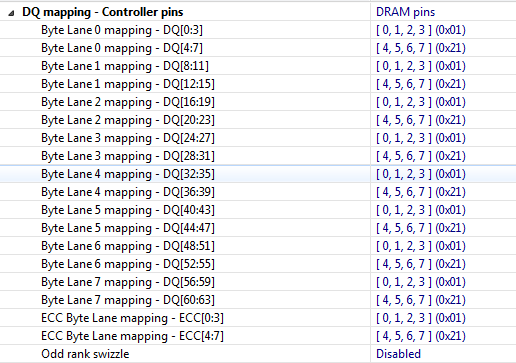

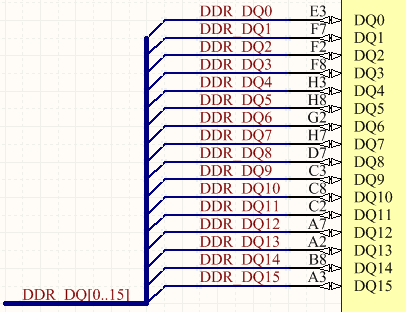

2) DDR controller DQ mapping settings correspond to the schematics

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks ufedor.

1) RESET to the DDR SDRAM chips is applied correctly

DDR Chips' reset is asserted with PORESET_B signal and de-asserted with HRESET signal. Although the board is meeting minimum timing requirement of CKE (i.e. CKE must remain low for at least 500us after chips' RESET is de-asserted), the CKE signal remains low for at least 2.5 seconds and then goes high continuously.

2) DDR controller DQ mapping settings correspond to the schematics

Our routing is done on 1-1 basis on all 10 chips, so mapping settings also seem to be correct as shown below:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What are the DDR controller registers values?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please check following settings. Our board has 2 chipselects but we are testing for 1 chipselect only just to troubleshoot the issue:

# DDR_SDRAM_CFG mem i:0xFE008110 = [value_of 0x67240000] # CS0_BNDS mem i:0xFE008000 = [value_of 0x010001FF] # CS1_BNDS mem i:0xFE008008 = [value_of 0x020002FF] # CS2_BNDS mem i:0xFE008010 = [value_of 0x0300033F] # CS3_BNDS mem i:0xFE008018 = [value_of 0x0340037F] # CS0_CONFIG mem i:0xFE008080 = [value_of 0x80014402] # CS1_CONFIG mem i:0xFE008084 = [value_of 0x00010202] # CS2_CONFIG mem i:0xFE008088 = [value_of 0x0202] # CS3_CONFIG mem i:0xFE00808C = [value_of 0x0202] # CS0_CONFIG_2 mem i:0xFE0080C0 = [value_of 0x00] # CS1_CONFIG_2 mem i:0xFE0080C4 = [value_of 0x00] # CS2_CONFIG_2 mem i:0xFE0080C8 = [value_of 0x00] # CS3_CONFIG_2 mem i:0xFE0080CC = [value_of 0x00] # TIMING_CFG_3 mem i:0xFE008100 = [value_of 0x000B0000] # TIMING_CFG_0 mem i:0xFE008104 = [value_of 0x4044000C] # TIMING_CFG_1 mem i:0xFE008108 = [value_of 0xB3BE3A75] # TIMING_CFG_2 mem i:0xFE00810C = [value_of 0x0030D116] # DDR_SDRAM_CFG_2 mem i:0xFE008114 = [value_of 0x00401810] # DDR_SDRAM_MODE mem i:0xFE008118 = [value_of 0x00061A40] # DDR_SDRAM_MODE_2 mem i:0xFE00811C = [value_of 0x00080000] # DDR_SDRAM_MODE_2 mem i:0xFE00811C = [value_of 0x00080000] # DDR_SDRAM_MODE_2 mem i:0xFE00811C = [value_of 0x00080000] # DDR_SDRAM_MODE_3 mem i:0xFE008200 = [value_of 0x00] # DDR_SDRAM_MODE_4 mem i:0xFE008204 = [value_of 0x00] # DDR_SDRAM_MODE_5 mem i:0xFE008208 = [value_of 0x00] # DDR_SDRAM_MODE_6 mem i:0xFE00820C = [value_of 0x00] # DDR_SDRAM_MODE_7 mem i:0xFE008210 = [value_of 0x00] # DDR_SDRAM_MODE_8 mem i:0xFE008214 = [value_of 0x00] # DDR_SDRAM_MD_CNTL mem i:0xFE008120 = [value_of 0x00000000] # DDR_SDRAM_INTERVAL mem i:0xFE008124 = [value_of 0x1034040D] # DDR_DATA_INIT mem i:0xFE008128 = [value_of 0xDEADBEEF] # DDR_SDRAM_CLK_CNTL mem i:0xFE008130 = [value_of 0x02800000] # DDR_INIT_ADDR mem i:0xFE008148 = [value_of 0x00000000] # DDR_INIT_EXT_ADDR mem i:0xFE00814C = [value_of 0x00000000] # TIMING_CFG_4 mem i:0xFE008160 = [value_of 0x01] # TIMING_CFG_5 mem i:0xFE008164 = [value_of 0x03401400] # DDR_ZQ_CNTL mem i:0xFE008170 = [value_of 0x89080600] # DDR_WRLVL_CNTL mem i:0xFE008174 = [value_of 0x8655F60D] # DDR_SR_CNTR mem i:0xFE00817C = [value_of 0x00000000] # DDR_WRLVL_CNTL_2 mem i:0xFE008190 = [value_of 0x00] # DDR_WRLVL_CNTL_3 mem i:0xFE008194 = [value_of 0x00] # DDR_ERR_DISABLE mem i:0xFE008E44 = [value_of 0x00] # DDR_ERR_INT_EN mem i:0xFE008E48 = [value_of 0x1D] # DDR_ERR_SBE mem i:0xFE008E58 = [value_of 0x00010000] # DDRCDR_1 mem i:0xFE008B28 = [value_of 0x80040000] # DDRCDR_2 mem i:0xFE008B2C = [value_of 0x01] # DDR_SDRAM_CFG_3 mem i:0xFE008260 = [value_of 0x00] # TIMING_CFG_6 mem i:0xFE008168 = [value_of 0x00] # TIMING_CFG_7 mem i:0xFE00816C = [value_of 0x00] # TIMING_CFG_8 mem i:0xFE008250 = [value_of 0x00] # DESKEW_CNTL mem i:0xFE0082A0 = [value_of 0x00] # DQ_MAP0 mem i:DDRmc1_DQ_MAP0_ADDR = [value_of 0x06106104] # DQ_MAP1 mem i:DDRmc1_DQ_MAP1_ADDR = [value_of 0x84184184] # DQ_MAP2 mem i:DDRmc1_DQ_MAP2_ADDR= [value_of 0x06106104] # DQ_MAP3 mem i:DDRmc1_DQ_MAP3_ADDR = [value_of 0x84184000] # DDR_SDRAM_MODE_9 mem i:0xFE008220 = [value_of 0x00] # DDR_SDRAM_MODE_10 mem i:0xFE008224 = [value_of 0x00] # DDR_SDRAM_MODE_11 mem i:0xFE008228 = [value_of 0x00] # DDR_SDRAM_MODE_12 mem i:0xFE00822C = [value_of 0x00] # DDR_SDRAM_MODE_13 mem i:0xFE008230 = [value_of 0x00] # DDR_SDRAM_MODE_14 mem i:0xFE008234 = [value_of 0x00] # DDR_SDRAM_MODE_15 mem i:0xFE008238 = [value_of 0x00] # DDR_SDRAM_MODE_16 mem i:0xFE00823C = [value_of 0x00] # DDR_SDRAM_RCW_3 mem i:0xFE0081A0 = [value_of 0x00] # DDR_SDRAM_RCW_4 mem i:0xFE0081A4 = [value_of 0x00] # DDR_SDRAM_RCW_5 mem i:0xFE0081A8 = [value_of 0x00] # DDR_SDRAM_RCW_6 mem i:0xFE0081AC = [value_of 0x00] #Delay before enable wait 500 #DDR_SDRAM_CFG mem i:0xFE008110 = [value_of 0xE7240000]

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please provide the processor connection schematics for inspection as searchable PDF.

To do that it will be convenient to create a Technical Case:

1) open www.nxp.com

2) Select "Support" -> "All Support Options"

3) Click "Go to Tickets"

4) Log in with your NXP login and password

5) On the "Group, Create and View your support cases" page press "+ Add a new case" to start the process.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have a case already opened regarding DDR bringup issue. Should I add these details to that case or open a new case for you?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please add the details to the Case.