- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- PBL stops loading before End Command

PBL stops loading before End Command

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

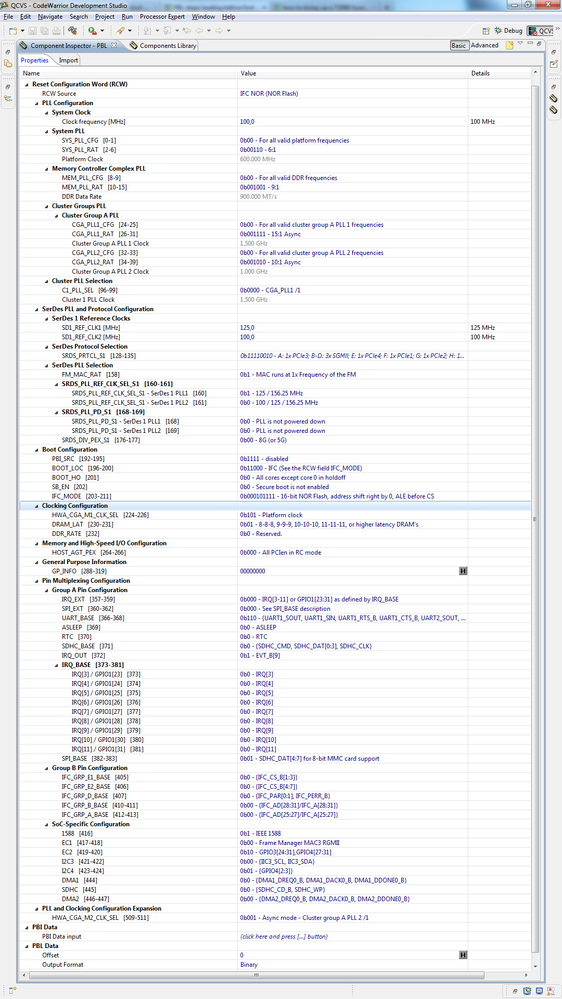

we have a new T2081 based cpu board and try to load RCW and U-Boot from nor flash. I can see that the PBL reads the preamble and RCW data (36*16Bit). But the PBL stops after reading the RCW and does not read the End Command. The data format should be ok since I used CodeWarrior Dev Studio to create the data and I checked the created data.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We had pull-downs connected to IFC_AVD and IFC_WP0_B. There is a note in T2081 data sheet that this pins must not be pulled down during power-on reset. After we changed these pull-downs to pull-ups the PBL works as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does the PBL use a flush command? The SDK and u-boot/pblimage used to use it until this restriction was put in place:

"Use of the Flush command is restricted to CCSR space. Software must use the Wait command after commands to non-CCSR space to allow them time to complete before issuing subsequent commands to non-CCSR space."

Ed Swarthout

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No Flush command. We don't have any PBI data at all (PBI_SRC=disabled), just the RCW.

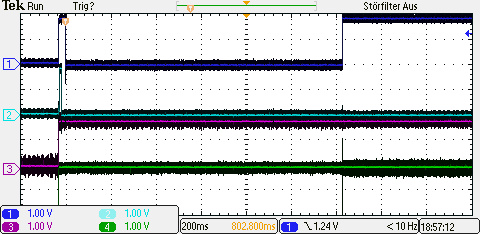

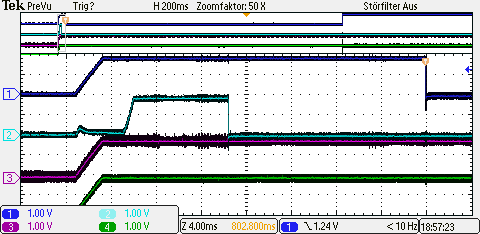

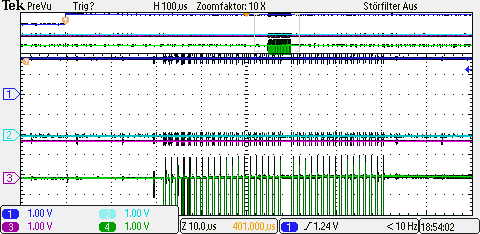

From measuring reset signals and cs0 (see above) I know that the cpu reads preamble and rcw. But the cpu never deasserts the HRESET signal and the end command is never read.

I already compared the signals with an T2080 eval board. From that and FTF-NET-F0152.pdf I know that pll should lock (according to the ratios specified in rcw) before HRESET is deasserted and end command is read. But I cannot find any errors in our rcw settings or input clocks.

Are there any other reasons beside the plls/input clocks which could cause this?

Our system controll FPGA needs some time before it can drive/assert PORESET (see pics above). Could this be a problem (it looks like CPU asserts HRESET before we assert PORESET)?

Ralf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We had pull-downs connected to IFC_AVD and IFC_WP0_B. There is a note in T2081 data sheet that this pins must not be pulled down during power-on reset. After we changed these pull-downs to pull-ups the PBL works as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found an interesting document about the QorIQ pre-boot loader:

http://cache.freescale.com/files/training/doc/ftf/2014/FTF-NET-F0152.pdf -> PBL in the Power Up Sequence

So I think sequence is something like this:

- reading the rcw data

- pll should lock according to the ratios specified in rcw

- hreset release

- PBL finishes the PBI

I checked my rcw settings but unfortunately still no success. I did some measurement and found that hreset is never released.

Are there any reasons beside the pll locks which could cause this?

hreset is asserted before poreset. Is this normal (our reset logic sets hreset to tri-state)?

Reset Signals (PORESET=dark blue, HRESET=light blue, HRESET_REQ=pink, CS0=green):

Details:

CS0 RCW:

My RCW Settings: